Synopsys has expanded its ARC processor portfolio to include a family of RISC-V processors. This was originally reported on SemiWiki last October. There is also a recent in-depth article on the make-up of the ARC-V family on SemiWiki here. This is important and impactful news; I encourage you to read these articles if you haven’t… Read More

Synopsys Accelerates Innovation on TSMC Advanced Processes

We all know that making advanced semiconductors is a team sport. TSMC can innovate the best processes, but without the right design flows, communication schemes and verified IP it becomes difficult to access those processes. Synopsys recently announced some details on this topic. It covers a lot of ground. The graphic at the top… Read More

SoC Power Islands Verification with Hardware-assisted Verification

The ever-growing demand for longer battery life in mobile devices and energy savings in general have pushed power optimization to the top of designers’ concerns. While various techniques like multi-VT transistors and clock gating offer power savings at gate-level design, the real impact occurs at system level, where hardware… Read More

ARC-V portfolio plus mature software IP targets three tiers

Synopsys is bridging its long-running ARC® processor IP strategy into a RISC-V architecture – Bernard Murphy introduced the news here on SemiWiki last November. We’re getting new insight from Synopsys on its ARC-V™ portfolio and how they see RISC-V IP plus their mature software development toolchain IP fitting customer needs… Read More

Synopsys is Paving the Way for Success with 112G SerDes and Beyond

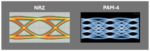

Data communication speeds continue to grow. New encoding schemes, such as PAM-4 are helping achieve faster throughput. Compared to the traditional NRZ scheme, PAM4 can send twice the signal by using four levels vs. the two used in NRZ. The diagram at the top of this post shows the how data density is increased. With progress comes… Read More

Podcast EP221: The Importance of Design Robustness with Mayukh Bhattacharya

Dan is joined by Mayukh Bhattacharya, Engineering, Executive Director, at Synopsys. Mayukh has been with Synopsys since 2003. For the first 14 years, he made many technical contributions to PrimeSim XA. Currently, he leads R&D teams for PrimeSim Design Robustness and PrimeSim Custom Fault products. He was one of the early… Read More

Lifecycle Management, FuSa, Reliability and More for Automotive Electronics

Synopsys recently hosted an information rich-webinar, modestly titled “Improving Quality, FuSa, Reliability, and Security in Automotive Semiconductors”. I think they undersold the event; this was really about managing all of those things through the lifecycle of a car, in line with auto OEMs strategies for the future of the… Read More

Podcast EP219: How Synopsys Addresses Debug and Coverage Closure Challenges with Robert Ruiz

Dan is joined by Robert Ruiz, product management director responsible for strategy and business growth of several verification products at Synopsys. Robert has held various marketing and technical positions for leading functional verification and test automation products at various companies including Synopsys, Novas… Read More

Semi Market Decreased by 8% in 2023… When Design IP Sales Grew by 6%!

Design IP revenues had achieved $7.04B in 2023, with disparity between license, growing by 14% and royalty decreasing by 6%, and main categories. Processor (CPU, DSP, GPU & ISP) slightly growing by 3.4% when Physical (SRAM Memory Compiler, Flash Memory Compiler, Library and I/O, AMS, Wireless Interface) slightly decreasing… Read More

Early SoC Dynamic Power Analysis Needs Hardware Emulation

The relentless pursuit for maximizing performance in semiconductor development is now matched by the crucial need to minimize energy consumption.

Traditional simulation-based power analysis methods face insurmountable challenges to accurately capture complex designs activities in real-world scenarios. As the scale… Read More