At the VLSI Technology Symposium Imec presented on Buried Power Rails (BPR) and Backside Power Delivery (BSPD) in a paper entitled: “Scaled FinFETs Connected by Using Both Wafer Sides for Routing via Buried Power Rails”. I recently had a chance to interview one of the authors, Naoto Horiguchi about the work. I have interviewed … Read More

ASML EUV Update at SPIE

At the 2022 SPIE Advanced Lithography Conference, ASML presented an update on EUV. I recently had a chance to go over the presentations with Mike Lercel of ASML. The following is a summary of our discussions.

0.33 NA

The 0.33 NA EUV systems are the production workhorse systems for leading edge lithography today. 0.33 NA systems are… Read More

CHIPS for America DOA?

- We think hopes for CHIPS for America is fading fast

- Politics, Jan 6th, guns, inflation, partisanship will likely block it

- Alternative to building US semis is knocking down China chips

- The only political option may be more restrictions on China

Chips for America act seems drowned out by partisan screaming

We have been saying, for… Read More

Semiconductors Weakening in 2022

The semiconductor market in 2022 is weakening. Driving factors include rising inflation, the Russian war on Ukraine, COVID-19 related shutdowns in China, and lingering supply chain issues. Four of the top 14 semiconductor companies (Intel, Qualcomm, Nvidia and Texas Instruments) are expecting lower revenues in 2Q 2022 versus… Read More

Stop-For-Top IP Model to Replace One-Stop-Shop by 2025

…and support the creation of successful Chiplet business

The One-Stop-Shop model has allowed IP vendors of the 2000’s to create a successful IP business, mostly driven by consumer application, smartphone or Set-Top-Box. The industry has dramatically changed, and in 2020 is now driven by data-centric application (datacenter,… Read More

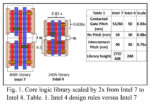

Intel 4 Deep Dive

As I previously wrote about here, Intel is presenting their Intel 4 process at the VLSI Technology conference. Last Wednesday Bernhard Sell (Ben) from Intel gave the press a briefing on the process and provided us with early access to the paper (embargoed until Sunday 6/12).

“Intel 4 CMOS Technology Featuring Advanced FinFET Transistors… Read More

Closing the Communication Chasms in the SoC Design and Manufacturing Supply Chain

In sports, we’re all familiar with how even a team with the best individual players for every role needs to be coordinated as a team to win a championship. In healthcare, a patient is better served with a well-trained primary physician to coordinate with the various medical specialists. The field of semiconductors involves a series… Read More

Importance of an Analytics Platform Before Migrating to the Cloud

After many years of hesitancy to jump with both feet in, semiconductor companies are seriously considering implementing cloud strategies and making required investments. Their concern though is, how much investment is it going to take? Some of the block-and-tackle challenges they face in implementing a cloud strategy are … Read More

Intel to present Intel 4 process at the VLSI Technology Symposium

The VLSI Symposium on Technology & Circuits will be held in Hawaii from June 12th to June 17th. You can register for the conference here.

The tip sheet for the conference has been released and one thing that caught my eye is some data from the Intel 4 paper that Intel will be presenting at the conference.

Intel’s old roadmap had 14nm,… Read More

CEO Interview: Vaysh Kewada of Salience Labs

Vaysh Kewada is cofounder and CEO at Salience Labs, a company developing an ultra high-speed multi-chip processor that packages a photonics chip together with standard electronics to enable exascale AI. Salience is funded by Oxford Sciences Enterprise, Cambridge Innovation Capital, Arm-backed Deeptech Labs, former Dialog… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center