Hardware is roaring back into prominence in technology innovation, from advanced cars to robots, smart homes and smart cities, 5G communication and the burgeoning electronification of industry, medicine and utilities. While software continues to play a role, all of these capabilities depend fundamentally on advances in … Read More

FPGA based Prototyping

Anirudh Keynote at CDNLive 2019

Anirudh Devgan (President of Cadence), gave the third keynote at CDNLive Silicon Valley this year. He has clearly become adept in this role. He has a big, but supportable vision for Cadence across markets and technologies and he’s become a master of the annual tech reveals that I usually associate with keynotes.

Anirudh opened … Read More

ARM, NXP Share Usage, Challenges at Synopsys Lunch

Synopsys runs a “Industry verifies with Synopsys” lunch at each DVCon, which isn’t as cheesy as the title might suggest. The bulk of the lunch covers user presentations on their use of Synopsys tools which I find informative and quite open, sharing problems as much as successes. This year, Eamonn Quiqley, FPGA engineering manager… Read More

Rapid Prototyping ARM Based Designs Webinar

While writing the definitive book on ARM history we could not have imagined a more different exit than the SoftBank acquisition, not even close. It is now very clear why SoftBank acquired ARM for $31B. It is also very clear why alternatives like RISC-V are trending on SemiWiki and will continue to do so, absolutely. No matter what … Read More

Cadence Automotive Summit Sensor Enablement Highlights

At the November 14 Cadence Automotive Summit, Ian Dennison, Senior Group Director, outlined sensor enablement technologies and SoC mixed-signal design solutions, from Virtuoso electrically aware design with high current, high reliability, yield and performance tools and methodologies enabling ADAS/AV sensors for vehicle… Read More

The Importance of Daughter Cards in FPGA Prototyping

FPGA Prototyping started with the advent of FPGAs in the 1980s and today it is a fast growing market segment due to increasing chip and IP complexities up against tightening windows of opportunities. Getting your design verified quickly and allowing hardware and software engineers the opportunity to develop, test, and optimize… Read More

1-on-1 with Anirudh Devgan, President, Cadence

At the Design Automation Conference, no one is busier than an EDA company executive — conference panels, product launch briefings, customer meetings, and corporate dinners all place considerable demands on their time. I was fortunate enough to be able to meet with Anirudh Devgan, President of Cadence, at the recent DAC55 in San… Read More

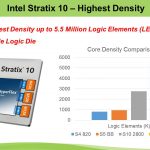

Intel Based FPGA Prototyping Webinar Replay

Due to the overwhelming response, here is the first part of the webinar that I did with S2C and a link to the replay. Richard Chang, Vice President of Engineering at S2C did the technical part of the webinar. Richard has a Masters degree in Electrical engineering from the University at Buffalo and more than 20 years experience designing… Read More

FPGA Prototyping Speeds Design Realization for the Internet of Things

When we talk about the Internet of Things (IoT), it isn’t a stretch to say that every intelligent device we interact with will become connected, sharing vast amounts of data with one another to make our lives more efficient. It isn’t only consumers of smart home, infotainment, and wearable technologies that are driving the demand,… Read More

Vertical Prototyping with Intel FPGAs

It has been an article of faith in the design tools business that there’s little to be gained from targeting market verticals because as far as tools are concerned, all verticals have the same needs. Which is good in some respects; you maximize the breadth of the market to which tooling can appeal. But in so doing the depth of contribution… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?