If we check the many articles daily published in Semiwiki, I am sure that Moore’s Law has been mentioned every single day. There is a good reason why we constantly write about new technologies and advanced features like FinFet, FD-SOI, 450 mm wafers or double patterning: all of these are new challenges that the SC industry will have… Read More

Searching an ADC (or DAC) at 28 nm may be such a burden…

If you have ever send a Request For Quotation (RFQ) for an ASIC including processor IP core, memories, Interfaces IP like PCIe, SATA or USB and Analog function like Analog to Digital Converter (ADC) or Digital to Analog Converter (DAC), you have discovered, like I did a couple of years ago, that these Analog functions may be the key… Read More

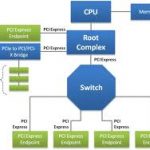

Mobile SoC will benefit now from M-PCIe

We have already discussed the recently released M-PCIe ECN from PCI-SIG in Semiwiki at the end of 2012, but the new “standard” (in fact an Engineering Change from PCI-SIG and MIPI Alliance) was only real on paper, at that time. The upcoming webinar from Synopsys, M-PCIe: Utilizing Low-Power PCI Express in Mobile Designs, shows … Read More

How to Benchmark a Processor

How do you benchmark a processor? It seems like it should be easy, just run some code and see how fast it is. Traditionally processors were indeed benchmarked by raw performance like GMACS, GFLOPS, memory bandwidth and so on. But in today’s world where systems have become very complex and applications very compute intensive, the… Read More

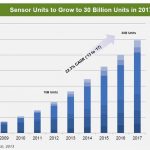

Pre-verified, Integrated Sensor IP Subsystem?

Last year, I said that the launch of ARC based complete sound system IP by Synopsys ring the bell for the opening of a new IP market segment, the “Subsystem IP”. This week, Synopsys has announced the availability of the DesignWare® Sensor IP Subsystem, a complete and integrated hardware and software solution for sensor control applications.… Read More

♫ IMG Sitting on the DOK of the Bay…Closin’ Timin’

Scott Fitzgerald is supposed to have said “the rich are not like other people” to Ernest Hemingway (he didn’t). In the same way, processors are not like other blocks, and not because they have more gates (they don’t). However, special approaches to optimizing processors are important because the clock… Read More

Debugging Verification Constraints

In his DAC keynote last year (2012) Mike Mueller of ARM compared how much CPU was required to verify the first ARM versus one of the latest ARM Cortex CPUs. Of course the newer CPU is hundreds of times larger than the first ARM but the amount of verification required was millions of times as much, requiring ARM to construct their own datacenter… Read More

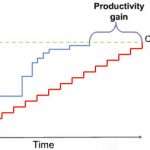

Can we really find a way to speed-up Processor & DSP core designs?

Once upon a time, ASIC designers involved in Processor design, like I was, for the first time in 1987 for Thomson CSF and again in 1994 for Texas Instruments, at that time supporting height (8) ASIC designed by another French company, the Advanced Computer Research Institute (ACRI), had to re-invent the wheel almost every day. When… Read More

Are you going to the plug fest?

PCI Express 3.0 specification is 1000 pages long. Most of us, and most of the designers integrating PCIe gen-3 into their latest ASIC, FPGA or system will probably never read it completely, or even open it. In fact, they don’t need to read it completely, but they should care about one point, whether they buy an ASSP or a PCIe design IP:… Read More

Happy Birthday to Synopsys VIP

I met Mike Sanie around DVCon time and planned to write a blog about the one year anniversary of Synopsys Discovery VIP which was announced during Aart’s keynote at DVCon in 2012. Eric covered it for SemiWiki here. But Synopsys had other stuff they wanted me to blog about and so it is a couple of months late. The 14th month anniversary… Read More