SemiWiki has been tracking the popularity of chiplets for two years now so it was not surprising to see that they played a key role at DAC. The other trend we foresaw was that the ASIC companies would be early chiplet adopters and that has proven true. One of the more vocal proponents of chiplets at DAC#59 was OpenFive, a 17+ year spec-to-silicon… Read More

Semiconductor Intellectual Property

Scalability – A Looming Problem in Safety Analysis

Scalability – A Looming Problem in Safety Analysis

The boundless possibilities of automation in cars and other vehicles have captivated designers to the point that electronic content is now a stronger driver of differentiation than any other factor. It accounts for a substantial fraction of material cost in any of these vehicles.… Read More

Arm Aims at Mobile Gaming

Clearly unfazed by the collapse of the proposed merger with Nvidia, Arm just announced products in support of, what else, mobile gaming. Nvidia turf. Of course Nvidia’s gaming strength is in tethered platforms or laptops. However, understand that 50% of video gaming revenue in 2020 came from smartphone games and that growth is… Read More

Memory Security Relies on Ultra High-Performance AES-XTS Encryption/Decryption

A recent SemiWiki post covered the topic of protecting high-speed interfaces in data centers using security IP. That post was based on a presentation made by Dana Neustadter at IP-Soc Silicon Valley 2022 conference. Dana’s talk was an overview of various interfaces and Synopsys’ security IP for protecting those interfaces. … Read More

Interface IP in 2021: $1.3B, 22% growth and $3B in 2026

If you want to remember the key points for Interface IP in 2021, just consider $1.3B, 22%, $3B. Interface IP category has generated $1 billion 300 million in 2021, or 22.7% year to year growth, thanks to high runner protocols PCIe, DDR memory controller and Ethernet/SerDes. Even more impressive is the forecast, as IPnest predict… Read More

CEO Interview: Barry Paterson of Agile Analog

Barry Paterson is the CEO of UK-based analog IP pioneer, Agile Analog. He has held senior leadership, engineering and product management roles at Dialog Semiconductor and Wolfson Microelectronics. He has been involved in the development of custom, mixed-signal silicon solutions for many of the leading mobile and consumer … Read More

5G for IoT Gets Closer

Very recently, 3GPP announced that 5G Release 17 was finalized. One important consequence is that 5G RedCap (reduced capacity) is now real and that means 5G becomes accessible to IoT devices. Think smart wearables (e.g. watches), industrial sensors and surveillance devices. “So what?”, you protest. “I don’t need 5G on my watch.… Read More

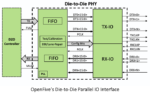

Verifying Inter-Chiplet Communication

Chiplets are hot now as a way to extend Moore’s Law, dividing functionality across multiple die within a single package. It’s no longer practical to jam all functionality onto a single die in the very latest processes, exceeding reticle limits in some cases and in others straining cost/yield. This is not an academic concern. Already… Read More

Using an IDE to Accelerate Hardware Language Learning

Recently, in one of my regular check-ins with AMIQ EDA, I was pleased that they linked me up with an active customer. The resulting post summarized my discussion with three engineers from Kepler Communications Inc. They talked about using one of the AMIQ EDA products in the design of FPGAs for space-borne Internet connectivity.… Read More

Time is of the Essence for High-Frequency Traders

In the world of financial trading, nanoseconds count. The faster a trade can be accomplished, the more money a trader can make. Getting a trade in before a competitor also results in improved profits. What does this have to do with the partnership deal recently inked between Silicon Creations and Achronix? Plenty. The two companies… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center