I just read this very interesting article posted by Kurt Shuler from Arteris, describing the “History of SoC Interconnect Fabric” and explaining why the SC industry needs an advanced approach, named the “fourth phase of the Interconnect Fabric history” in the article. Kurt’s point of view is that in the past the SoC interconnect… Read More

Semiconductor Intellectual Property

Mobile-Ready EDA and Semi IP Web Sites

18 months ago I blogged about how the mobile revolution that we enjoy today is really enabled by EDA software and IP in the hands of SoC designers, yet very few EDA and Semi IP companies had mobile-ready web sites. In that past 18 months we’ve witnessed only a handful of companies migrate to mobile-friendly web sites, the most… Read More

A Big Thank You to EDA and IP

Electronic Design Automation Software and Semiconductor Intellectual Property are not so much the tail that wags the dog, rather they are like the heart of an elephant, tiny in comparison but without which there is no elephant. There is no doubt that EDA and IP have been key enablers of the semiconductor industry for the past 50 years… Read More

TSMC Open Innovation Platform Forum, October 1st

One of TSMC’s two big Silicon Valley events each year is the Open Innovation Platform (OIP) Forum. This year it is on Tuesday October 1st. It is in the San Jose Convention Center and starts at 9am (registration opens at 8am). Pre-registration to attend is now open here or click on the image to the right.

From 9.10 to 9.40 is the … Read More

What Does Sports and NoC Have in Common?

As an Oakland Raider season ticket holder I attend as many Raider home games as possible. If you have ever attended a live sporting event at a large stadium, and you travelled by car, you are probably familiar with the traffic problems that occur at the end of the game when everyone wants to leave the stadium parking lot at the same time.… Read More

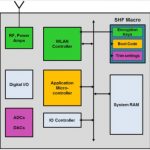

Using OTP Memories To Keep SoC Power Down

Virtually all SoCs require one-time programmable (OTP) memory. Each SoC is different, of course, but two main uses are large memories for holding boot and programming code and small memories for holding encryption keys and trimming parameters, such as radio tuning information and so on.

There are alternatives to putting an OTP… Read More

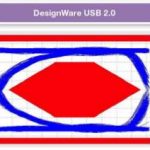

Interface PHY IP supporting Mobile Application on TSMC 20nm? Available!

If we check the many articles daily published in Semiwiki, I am sure that Moore’s Law has been mentioned every single day. There is a good reason why we constantly write about new technologies and advanced features like FinFet, FD-SOI, 450 mm wafers or double patterning: all of these are new challenges that the SC industry will have… Read More

Texture decompression is the point for mobile GPUs

In the first post of this series, we named the popular methods for texture compression in OpenGL ES, particularly Imagination Technologies PVRTC on all Apple and many Android mobile devices. Now, let’s explore what texture compression involves, what PVRTC does, and how it differs from other approaches.… Read More

How Do You Do Computational Photography at HD Video Rates?

Increasingly, a GPU is misnamed as a “graphics” processing unit. They are really specialized architecture highly parallel compute engines. You can use these compute engines for graphics, of course, but people are inventive and find ways of using GPUs for other tasks that can take advantage of the highly parallel… Read More

TSMC’s 16FinFET and 3D IC Reference Flows

Today TSMC announced three reference flows that they have been working on along with various EDA vendors (and ARM and perhaps other IP suppliers). The three new flows are:

- 16FinFET Digital Reference Flow. Obviously this has full support for non-planar FinFET transistors including extraction, quantized pitch placement, low-vdd

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!