The Common Platform Alliance — IBM, Samsung Electronics, Co., Ltd., and GLOBALFOUNDRIES — continues to redefine the landscape of the semiconductor industry with its groundbreaking collaboration. Join us at our 2013 Common Platform Technology Forumon Tuesday, February 5, 2013 at the Santa Clara Convention Center as we showcase… Read More

Semiconductor Intellectual Property

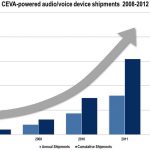

Audio/Voice DSP IP core: the next road to billion unit shipment

When mentioning CEVA DSP IP cores, the first reaction is to think about the complexes DSP functions used into wireless Modem Application like 3G and Long Term Evolution (LTE). Considering that CEVA market share is above 70% for these products, such a reaction makes sense. But did you knew that CEVA DSP IP cores are also empowering… Read More

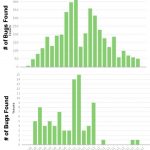

Formal Verification at ARM

There are two primary microprocessor companies in the world these days: Intel and ARM. Of course there are many others but Intel is dominant on the PC desktop (including Macs) and ARM is dominant in mobile (including tablets).

One of the keynotes at last month’s Jasper User Group (JUG, not the greatest of acronyms) was by Bob… Read More

Cortex-A9 speed limits and PPA optimization

We know by now that clock speeds aren’t everything when it comes to measuring the goodness of a processor. Performance has direct ties to pipeline and interconnect details, power factors into considerations of usability, and the unspoken terms of yield drive cost.

My curiosity kicked in when I looked at the recent press release… Read More

New HP Memristor Material Developments

At the recent NCCAVS Thin Film Users Group meeting in November, HP was on the program in the person of Joshua Yang who gave a materials centric look at the status of the HP ReRAM (Memristor) program. A colleague passed on the informative set of slides presented at the meeting. Being a former process integration team leader, I was immediately… Read More

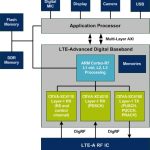

When ARM and CEVA team-up for “Designing a Multi-core LTE-A Modem”

ARM and CEVA have launched a white paper, addressing one of the hottest topics of the day: LTE-Advanced modem architecture. This very exhaustive paper, written by David Maidment (Mobile Segment Manager, ARM), Chris Turner (Senior Product Manager, ARM) and Eyal Bergman (VP Product Marketing, Baseband & Connectivity, CEVA… Read More

How Apple Plans to Leverage Intel’s Foundry

Tim Cook’s strategy to disengage from Samsung as a supplier of LCDs, memory and processors while simultaneously creating a worldwide supply chain from the remnants of former leaders like Sharp, Elpida, Toshiba and soon Intel is remarkable in its scope and breadth. By 2014, Apple should have in place a supply chain for 500M iOS devices… Read More

A Brief History of the MIPS Architecture

MIPS is one of the most prolific, longest-living industry-standard processor architectures, existing in numerous incarnations over nearly three decades.

MIPS has powered products including game systems from Nintendo and Sony; DVRs from Dish Network, EchoStar and TiVo; set-top boxes from Cisco and Motorola; DTVs from Samsung… Read More

Subsystem IP, myth or reality?

I have participated to a panel during IP-SoC, I must say that “Subsystem IP, myth or Reality” was a great moment. The panel was a mix of mid-size IP vendor (CAST, Sonics), one large EDA (Martin Lund from Cadence), Semiwiki blogger and one large IDM (Peter Hirt from STM) who has very well represented the customer side. And, to make the… Read More

A Brief History of the Fabless Semiconductor Ecosystem

Clearly the fabless semiconductor ecosystem is driving the semiconductor industry and is responsible for both the majority of the innovation and the sharp decline in consumer electronics costs we have experienced. By definition, a fabless semiconductor company does not have to spend the time and money on manufacturing related… Read More

Huawei’s and SMIC’s Requirement for 5nm Production: Improving Multipatterning Productivity