Last week I wrote about NetSpeed’s network on chip (NoC) IP technology and design environment NocStudio. This week we see a real life application of this technology announced at CES by Imagination Technologies and NetSpeed. The companies have announced that Mobileye will use Imagination and NetSpeed IP in their next-generation… Read More

Semiconductor Intellectual Property

Analog Bits and TSMC!

As a long time semiconductor IP professional I can tell you for a fact that it is one of the most challenging segments of semiconductor design. Given the growing criticality of semiconductor IP, the challenges of being a leading edge IP provider are increasing and may be at a breaking point. The question now is: What does it take to … Read More

Intelligent Vision in (almost) Every Application

Let’s take a look at the tremendous penetration of intelligent vision in so many and various applications. A few years ago, computer vision algorithms were implemented in applications directly linked with imaging, like computational photography for smartphones and cameras. We can mention today a bunch of segments like automotive,… Read More

Webinar: Hassle-Free Bluetooth 5 SoC Design

Bluetooth has always been a popular communication protocol for short-range applications, but now anticipating BT5 it’s really moving into the big leagues as a significant option for IoT applications. The new standard combines ultra-low power with significantly higher range and higher performance. Ultra-low power is always… Read More

Dassault Systemes Hosts New Microsite Focused on IP Reuse Challenges

I recently wrote an article about networks-on-chip (NoC) and how Systems-On-Chip integrated circuits (SoCs) are becoming increasingly more complex and heterogeneous in nature. While researching for that article I came upon a new micro-site by Dassault Systemes that goes into great detail about the operational challenges… Read More

Executive Interview: Joe Rowlands, Chief Architect at NetSpeed Systems

Joe has devoted his career to understanding and designing cache coherent systems and has been granted over 95 patents on the subject. For the past four years, he has been Chief Architect at NetSpeed, a developer of network-on-chip SoC interconnect.… Read More

Intel Spreadtrum ARM SoCs

In June of 2013 Edward Snowden copied and leaked classified information from the National Security Agency (NSA). His actions exposed numerous surveillance programs that many governments around the world reacted to, including China. In September of 2013 China Vice Premier Ma Kai declared semiconductors a key sector for the … Read More

Moving from SRAM to DDR DRAM in Safety Critical Automotive Systems

Until now, most of the processors contained within automobiles could be served by SRAM, at the exception of infotainment systems relying on a more powerful CPU connected to DRAM, but these systems are non-safety-critical. Advanced Driver Awareness Systems (ADAS) and self-driving vehicle systems demand powerful processors… Read More

ARM and Open Silicon Join Forces to Fight the IoT Edge Wars!

I spent the last several days doing a deep dive into the world of IoT security and what I’ve learned has scared the pants off me. Various analysts predict that there will be over 30 billion connected IoT devices by the year 2020 growing from 9.9 million in 2013. A quick audit of my home identified over 40 connected devices including everything… Read More

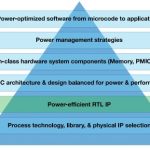

How ARM designs and optimizes SoCs for low-power

ARM has become such a worldwide powerhouse in delivering processors to the semiconductor IP market because they have done so many things well: IP licensing model, variety, performance, and low-power. On my desk are two devices with ARM IP, a Samsung Galaxy Note 4 smart phone and a Google tablet. Most of my readers will likely have… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era