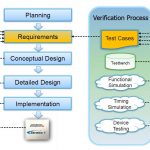

Word association: if I said “requirements management”, you’d probably say IBM Rational “DOORS,” or maybe Serena or Polarion if you come from the IT world. But what if the requirements you need to manage are for an FPGA or ASIC, with HDL and testbench code and waveform files and more details backing verification, and compliance… Read More

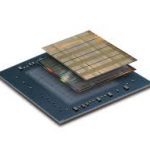

Prototyping Over 100 Million ASIC Gates Capacity

Most SoCs today are being prototyped in FPGA hardware before committing to costly IC fabrication. You could just design and build your own FPGA prototyping system, or instead choose something off the shelf and then concentrate on your core competence of SoC design.

Thanks to the FPGA vendors like Xilinx we now have FGPA prototyping… Read More

Are there enough FPGA tools?

Sometimes I send my boy to grab me a tool and hours later he comes back with the wrong one. The patient man that I am, I calmly explain what I mean and then the world is right once more. Believe that do ya?

As you know the world is flooded with tools, tools and more tools. We all have our ruts and favorite flows and such but given the huge FPGA … Read More

Which is the best FPGA – Xilinx

Your corporate training will teach you there is no such thing as stereo types and they are bad, naughty. We all know they are true; it’s just some companies now of days try to force the worker bees to do a flash erase and drop your brain at the door. I never participated in that and as you can imagine it went very well. Dilbert is true…

I am … Read More

Beyond one FPGA comfort zone

Unless you are a small company with one design team, the chance you have standardized on one FPGA vendor for all your needs, forever and ever, is unlikely. No doubt you probably have a favorite, because of the specific class of part you use most often or the tool you are most familiar with, but I’d bet you use more than one FPGA vendor routinely.… Read More

FPGAs – The Possibilities are Endless – Almost

Has your wife ever said “Your name, I’m not a computer”? Well maybe mine has. I know what you are thinking… This guy is married? Yup, I over achieved too. Have child #7 on the way Lord willing, so you probably guessed I don’t follow much of the world’s planning and such. Like you, no one in my house really understands what I do, nor cares … Read More

Morris Chang on Altera and Intel

If you want to know why I have written so much about TSMC in the past five years here it is: TSMC executives are approachable, personable, answer questions straight on, and have yet to lead me astray. If you want an example of this read the Chairman’s comments on the TSMC Q1 2013 earnings call transcript.

“On 16-nanometer FinFET, we … Read More

FPGA + MATLAB = FATLAB

Now Michael Bloomberg probably wouldn’t want FATLAB but let’s face it, to think like him you need a lot of education, alot. He may be banning 14nm because it will increase FPGAs densities and thus the consumer as well. Stay tuned. After some comments from my dear readers, one who said to watch it with respect to my harshness about… Read More

FPGAS – The New Single Board Computers?

I have always felt that FPGAs have been the red haired step child of Silicon Valley. Software weenies have hated them, they are mysterious and take too long to route. Even though they can be massively parallel and the most deterministic piece of silicon you can buy besides a million dollar ASIC, the GPU steals their glory, for now. … Read More

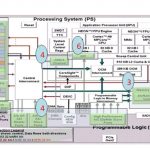

Xilinx: Hide the RTL

Tom Feist of Xilinx presented here at the GlobalPress Electronics Summit about their strategy to take design abstraction up another level. In the SoC world, we are still pretty much stuck at the RTL level and have moved to higher abstractions by using an IP strategy. But at least all IC designers are RTL-literate.

Xilinx, in the Vivado… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center