Handel Jones has a new white-paper out titled Why Migration to FD-SOI is a Better Approach Than Bulk CMOS and FinFETs at 20nm and 14/16nm for Price-Sensitive Markets. Handel has done an in-depth analysis of the wafer and die costs of the various approaches, bulk planar (what we have been doing up to now), FD-SOI and FinFET. The analysis… Read More

The Technology to Continue Moore’s Law…

Can we agree about the fact that the Moore’s law is discontinuing after 28nm technology node? This does not mean that the development of new Silicon technology, like 14nm or beyond, or/and new Transistor architecture like FinFET will not happen. There will be a market demand for chips developed on such advanced technologies: mobile… Read More

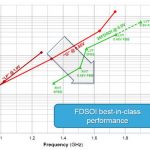

If you still think that FDSOI is for low performance IC only…

…then you should read about this benchmark result showing how digital power varies with process corners, for high-speed data networking chip, not exactly the type of IC targeting mid-performance mobile application. Before discussing the benchmark results, we need to have some background about this kind of ASIC chip. Such a … Read More

Why SOI is the Future Technology of Semiconductor

No doubt that FDSOI generate high interest these days and I found a very interesting contribution from Zvi Or-Bach, President and CEO of MonolithIC 3D, Inc. Zvi has accepted to share his wrap-up from IEDM, in a blog for Semiwiki readers. If you remember the long discussion we had in Semiwiki about cost comparison, some comments were… Read More

UTBB FDSOI Devices Featuring 20nm Gate Length

Did you go to IEDM 2013 in Washington DC ? You may have attended to the “Advanced CMOS Technology Platform” chaired by TSMC, and listen to the FD-SOI related presentation “High Performance UTBB FDSOI Devices Featuring 20nm Gate Length for 14nm Node and Beyond”. According with the abstract, this paper is the first time report of “high… Read More

FD-SOI Memories

When people discuss capabilities of leading edge process nodes they tend to focus on digital logic. Microprocessors in particular. But a process requires more than just digital logic and standard cells to be successful. In particular, pretty much every SoC contains a lot of memory so the memory capabilities of a process are important.… Read More

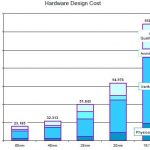

Could FD-SOI be Cheaper too?

We agree now that FD-SOI technology is Faster, Cooler, Simpler. But can it also be a cheaper technology? Let start with an overview of the current estimation of the development cost for complex SoC on advanced technology nodes. The following data are extracted from International Business Strategies, Inc 2013 report. The first… Read More

Is FD-SOI Really Faster, Cooler, Simpler?

I love the slogan associated with FD-SOI: the technology is supposed to be Faster, Cooler, Simpler. Does this slogan reflect the reality? Let’s start with Simpler. We (the semiconductor industry) have the perception that Silicon On Insulator (SOI) technology is something complex and exotic. Why? Because SOI has been used to … Read More

Is FD-SOI Smarter than Moore?

If you have read the excellent article from Paul McLellan, you know about FDSOI as a technology, so I will not come back to FDSOI device, and the comparison with FinFET in term of device topology, doping level and so on. If you missed it, I would recommend you to read this article, as well as the many comments (all of them being relevant).… Read More

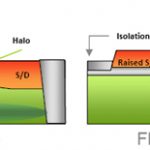

The Alternative to FinFET: FD-SOI

Everywhere you turn these days you find FinFETs. Intel has had them since 22nm (they use the word Tri-gate but it is the same as what the world calls FinFET) and TSMC will have them at 16nm. So why FinFET? And is there an alternative?

The reason that regular bulk planar transistors have run out of steam is that the channel area underneath… Read More