Aldec continues to claim a bigger seat at the table, most recently in their attendance at SC17, the supercomputing conference hosted last month in Denver. I’m really not sure how to categorize Aldec now. EDA company seems to miss the mark by a wide margin. Prototyping company? Perhaps, though they have a much stronger focus on end-applications… Read More

Going to CES 2018? Don’t Miss CEVA-powered Demos!

CES 2018 will start soon and will be held on January 9-12 in Las Vegas. If you plan to go to Vegas, don’t miss CEVA-powered smart and connected products and demos! CEVA’s product portfolio includes DSP IP cores (the smart) and RivieraWaves IP platforms supporting wireless protocols, like WiFi and Bluetooth (the connected).

DSP … Read More

Networking and Formal Verification

I attended Oski’s latest Decoding Formal event a couple of weeks ago and again enjoyed a largely customer-centric view of the problems to which they apply formal, and their experiences in making it work for them (with Oski help of course). From an admittedly limited sample of two of these events, I find them very representative of… Read More

CES Preview with Cadence!

The Consumer Electronics Show (CES) is in its 50th year believe it or not! The first one was in New York (1967) with 250 exhibitors and 17,500 attendees. Portable radios and TVs were all the rage followed by VCRs in 1970 and camcorders and compact discs in 1981. This year there will be 3,900+ exhibits and an estimated 170,000 attendees… Read More

Webinar: ADAS and Real-Time Vision Processing

ADAS is in many ways the epicenter of directions in the driverless car (or bus or truck). Short of actually running the car hands-free through a whole trip, ADAS has now advanced beyond mere warnings to providing some level of steering and braking control (in both cases for collision avoidance), providing more adaptive cruise control,… Read More

Free IoT SOC Books at REUSE 2017

The second annual REUSE conference is next week bringing the fabless semiconductor ecosystem together for a day of food, fun, and some very interesting presentations. It’s at the Santa Clara Convention Center this year which is nice and it is FREE! More importantly, there will be 30+ vendors in the exhibit hall which opens… Read More

Safety qualification for leading edge IP elements – presentation at REUSE 2017 in Santa Clara

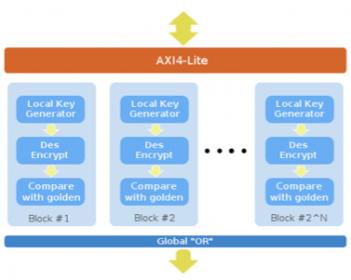

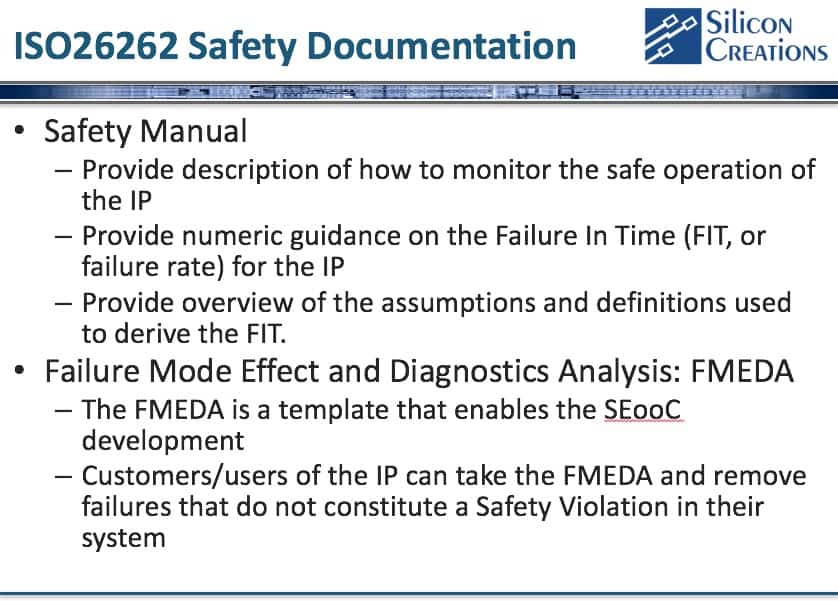

To ensure the reliability of automotive electronics, standards like AEC-Q100 and ISO 26262 have helped tremendously. They have created rational and explicit steps for developing and testing the electronic systems that go into our cars. These are not some abstract future requirement for fully autonomous cars, rather they are… Read More

35 Semiconductor IP Companies Hold 2nd Annual Conference

Our smart phone driven semiconductor economy consumes a lot of IP blocks to enable quick product development cycles, often annually updating with new models to choose from. So where do you find all of the best semiconductor IP, verification IP and embedded software? Well, one place is at the 2nd annual REUSE conference, scheduled… Read More

RISC-V Business

I was at the 7[SUP]th[/SUP] RISC-V Workshop for two days this week. It was hosted by Western Digital at their headquarters in Milpitas. If you have not been following RISC-V, it is an open source Instruction Set Architecture (ISA) for processor design. The initiative started at Berkeley, and has been catching on like wildfire. … Read More

IP-SoC 2017: IP Innovation, Foundries, Low Power and Security

The 20[SUP]th[/SUP] IP-SoC conference will be held in Grenoble, France, on December 6-7, 2017. IP-SoC is not just a marketing fest, it’s the unique IP centric conference, with presentations reflecting the complete IP ecosystem: IP suppliers, foundries, industry trends and applications, with a focus on automotive. It will … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry