I got an email from Mentor Embedded this morning about a webinar on Implementing a GENIVI-compliant System. I have to admit I had no idea what GENIVI is, which surprised me. I spent several years working in the embedded space and so I usually have at least a 50,000 foot view of most things going on there. One reason for my ignorance is … Read More

A DAC Update from Mentor Graphics on IC Layout and Circuit Simulation Tools

Linda Fosler, Tom Daspit and Mitch from Mentor Graphics met with me last Monday at DAC to provide an update on IC layout and circuit simulation tools. My notes follow:

Overview – Pyxis for Schematic and Layout, IC Station is re-branded as Pyxis. (Pyxis schematic is still Falcon, Ample language is still used.)… Read More

Mentor Graphics Update 2012!

What is new with Mentor? Quite a bit actually. About this time last year Corporate Raider Carl Icahn stirred things up with a hostile takeover attempt that ended with three Raiderettes on the Mentor Board, out of eight board members total. This year however, two of the three Raiderettes are out so it looks like Mentor is firmly in control.… Read More

Two New Board Members at Mentor Graphics

One year ago the annual share holder meeting at Mentor Graphics had tight security, a no-camera policy, and the drama of Carl Icahn the corporate raider successfully adding three new board members. Fast forward to today where two of Icahn’s board members were not even nominated, and Mentor added two new board members. I chatted… Read More

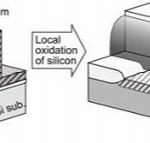

3D Transistors and IC Extraction Tools

Have you ever heard of a Super Pillar Transistor? It’s one of many emerging 3D transistor types, like Intel’s popular FinFET device.

In the race to continuously improve MOS transistors, these new 3D transistor structures pose challenges to the established IC extraction tool flows.

Foundries have to provide an Effective… Read More

View from the top: Michael Buehler-Garcia

Yesterday I met with Michael Buehler-Garcia, Director of Marketing at Mentor Graphics for Calibre in Wilsonville, Oregon to get an update on what’s coming up at DAC, the premier conference and trade show for our industry.

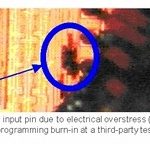

IC Reliability and Prevention During Design with EDA Tools

IC device physics uncovers limits to reliable operation, so IC designers are learning to first identify and then fix reliability issues prior to tape-out. Here’ s a list of reliability issues to keep you awake at night:… Read More

Mentor’s New Emulator

Mentor announced the latest version of their Veloce emulator at the Globalpress briefing in Santa Cruz. The announcement is in two parts. The first is that they have designed a new custom chip with twice the performance and twice the capacity. It supports up to two billion gate designs and many software engineers. Surprisingly … Read More

Changing your IC Layout Methodology to Manage Layout Dependent Effects (LDE)

Smaller IC nodes bring new challenges to the art of IC layout for AMS designs, like Layout Dependent Effects (LDE). If your custom IC design flow looks like the diagram below then you’re in for many time-consuming iterations because where you place each transistor will impact the actual Vt and Idsat values, which are now a … Read More

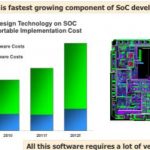

Doing what others don’t do

Wally Rhines’ keynote at U2U, the Mentor users’ group meeting, was about Mentor’s strategy of focusing on what other people don’t do. This is partially a defensive approach, since Mentor has never had the financial firepower to have the luxury of focusing all their development on sustaining their products and then make … Read More