Ground. It’s that little downward-pointing triangle that somehow works miracles on every schematic. It looks very simple until one has to tackle modern power distribution network (PDN) design on a board with high speed and high power draw components, and you soon discover ground is a complicated fairy tale with a lot of influences.… Read More

Mentor at TSMC Technology Symposium

TSMC will host their annual technology symposium at several locations in the U.S. on April 9th in San Jose, April 16th in Austin, and April 23rd in Boston. TSMC will discuss the market outlook, design enablement, and technology for high-speed computing, mobile communications, connectivity and storage, CIS, embedded flash, … Read More

New ways for High Frequency Analysis of IC Layouts

Amidst frequently changing requirements, time pressure and demand for high accuracy, it is imperative that EDA and design companies look at time consuming processes in the overall design flow and find alternatives without losing accuracy. High Frequency Analysis of IC designs is one such process which is traditionally based… Read More

Wally Rhines, Victor Peng and Chenming Hu to Speak at Mentor User2User Conference

This year’s Mentor Graphics user group meeting, User2User, will be held at the DoubleTree by Hilton in San Jose, California on April 25, 2013. The featured keynote presenters include…

- Dr. Walden C. Rhines, CEO and Chairman of Mentor Graphics, talking about “Organizing by Design”

- Victor Peng, Senior VP, Xilinx presenting on “The

EDAC CEOs: consolidation, clouds, and whether Intel will buy Synopsys

Yesterday evening was the annual EDAC CEO forecast meeting. Actually it is not really a forecast meeting any more, more a sort of CEO response to some survey questions asked of EDAC members. Rich Valera of Needham moderated with Lip-Bu, Aart and Wally, along with Simon Segars representing the IP arm(!) of the business and Raul Camposano… Read More

IJTAG for IP Test: a free seminar

What: Better IP Test with IJTAG

When: 26 March, 2013, 10:30am-1:30pm

Where: Mentor Graphics, 46871 Bayside Parkway, Fremont, CA 94538

If you are involved in IC test*, you’ve probably heard about the IEEE P1687 standard, called IJTAG for ‘internal’ JTAG. IJTAG defines a standard for embedded IP that includes simple… Read More

Standard Cell Library Characterization

Standard cell library characterization has been around for decades, Synopsys has been offering Liberty NCXand Cadence has Virtuoso Foundation IP Characterization. What’s new is that Mentor Graphics acquired the Z Circuit technology for library characterization and has integrated it with the Eldo Classic circuit … Read More

Verification the Mentor Way

During DVCon I met with Steve Bailey to get an update on Mentor’s verification. They were also announcing some new capabilities. I also attended Wally Rhines keynote (primarily about verification of course, since this was DVCon; I blogged about that here) and the Mentor lunch (it was pretty much Mentor all day for me) on the… Read More

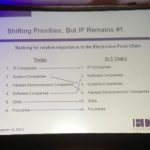

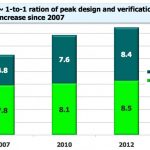

Wally Rhines: Name That Graph!

Wally Rhines gave the keynote at DVCon yesterday. He started out with a game of “name that graph” which was unfortunately a bit spoiled since when the names were revealed the first line was off the top of the screen. But he extrapolated several trends such as the decreasing number of fabs (the current trend is that there… Read More

How Can You Work Better with Your Foundry?

The fabless revolution in the digital semiconductor industry is no more, with just a few integrated device manufacturers (IDMs) remaining on the playing field, it is now the normal way to do business. However, the learning curve for each new process node continues as it always has, with a host of new technical challenges for the … Read More