You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 828

[filter] => raw

[cat_ID] => 159

[category_count] => 828

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 828

[filter] => raw

[cat_ID] => 159

[category_count] => 828

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

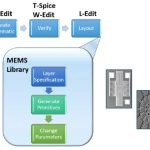

With the industry abuzz about the Apple purchase of a Maxim Integrated fab as a potential R&D facility for MEMS design, it begs the question: is creating a MEMS device that easy?

MEMS technology is approaching the same fork in the road where digital design encountered LSI four decades earlier. … Read More

I was kind of shocked when the service manager at our local VW dealership told me that one of the wires in the ignition system of my wife’s New Beetle had started to overheat, melting the insulation and becoming a safety hazard. Why didn’t a fuze just blow, protecting the wiring from overheating? We decided to quickly … Read More

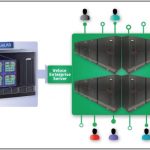

Software-centric Emulation environment takes the forefront in modern SoC verification. As more and more devices are IoT enabled, the SoCs have to make special provisions to factor many things including communication, power usage, and network switching, and so on. Also, the demand for an SoC (specifically for smartphone which… Read More

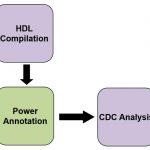

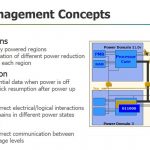

So far in my blog series on low power we’ve looked broadly at what’s changing in the low power verification landscape and focused on a new methodology developed by Mentor Graphics and ARM called successive refinement, which is now included in the UPF standard. Power management techniques create their own brand of clock domain crossing… Read More

Portable Stimulus has become such a popular standards topic of late that I thought it would be good to take a break this month from my low power series to bring you, my valued readers, more information about it from one of my colleagues, Dennis Brophy, who is working to help drive development of this standard within Accellera. I’ll … Read More

Walking into the Mentor Graphics booth at ARM TechCon, I was greeted by my friends Warren Kurisu and Shay Benchorin. It was good to see them both again. They were poised in front of a table with a Samsung tablet and a small Wi-Fi-ish box, next to a large Samsung printer. The demonstration was similar to a lobby check-in process, where… Read More

Power management is a perennial topic these days, and it came up in several presentations at the recent ARM Techcon in Santa Clara in mid November. The techniques covered in these talks address dynamic and static power consumption. The IEEE 1801 standard deals with specifying power design intent in Universal Power Format (UPF)… Read More

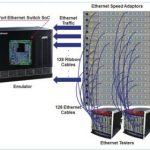

To fans of Godel, Escher and Bach (the Eternal Golden Braid), there is an appealing self-referential elegance to the idea of verifying a network switch in a cloud-like resource somewhere on the corporate network. That elegance quickly evaporates however when you consider the practical realities of verifying such device in ICE… Read More

Last week was the EDAC Phil Kaufman award dinner. It was much more like a roast, probably because Wally has a great sense of humor and as Aart de Geus said, “Wally is a cool cat to have a beer with…” Aart is right of course, hanging with Wally is one of my favorite work things to do.

The place was lousy with media people so I will try and add some… Read More

In a semiconductor industry which appears maturing, we are also seeing the technologies unravelling newer transistor structures, memories, processors, and newer ways of designing ICs and electronic systems. The present decade appears to be at the cusp of a new transformation in the semiconductor industry. Amid a slew of mergers… Read More