One of my favorite EDA disruptions is the Siemens acquisition of Mentor, pure genius. Joe Sawicki now runs the Mentor IC EDA business for Siemens so we will be seeing him at more conferences and events than ever before. Joe did a very nice keynote at the recent U2U conference that I would like to talk about before we head to the 56thDAC… Read More

EDA Update 2019

Over the last six years EDA has experienced yet another disruption not unlike the Synopsys acquisition of Avant! in 2001 which positioned Synopsys for the EDA lead they still enjoy today. Or the hiring of famed venture capitalist Lip-Bu Tan in 2009 to be the CEO of struggling EDA pioneer Cadence Design Systems. Under Lip-Bu’s… Read More

Deep Learning, Reshaping the Industry or Holding to the Status Quo

AI, Machine Learning, Deep Learning and neural networks are all hot industry topics in 2019, but you probably want to know if these concepts are changing how we actually design or verify an SoC. To answer that question what better place to get an answer than from a panel of industry experts who recently gathered at DVcon with moderator… Read More

User2User Silicon Valley 2019

This will be one of the more interesting Mentor User Group Meetings now that the Siemens acquisition has fully taken effect and the new management team is in place. The Mentor User Conference is at the Santa Clara Marriott, Santa Clara, California on May 2, 2019 from 9:00 am to 6:00pm.

Remember, in 2017 Siemens acquired Mentor Graphics… Read More

A Collaborative Driven Solution

Last week TSMC announced the availability of its complete 5nm design infrastructure that enables SoC designers to implement advanced mobile and high-performance computing applications for the emerging 5G and AI driven markets. This fifth generation 3D FinFET design infrastructure includes technology files, PDKs (Process… Read More

Functional Verification using Formal on Million Gate Designs

Verification engineers are the unsung heroes making sure that our smart phone chips, smart watches and even smart cars function logically, without bugs or unintended behavior. Hidden bugs are important to uncover, but what approach is best suited for this challenge?

With the Universal Verification Methodology (UVM) there’s… Read More

Hierarchical RTL Based ATPG for an ARM A75 Based SOC

Two central concepts have led to the growth of our ability to manage and implement larger and larger designs: hierarchy and higher levels of abstraction. Without these two approaches the enormous designs we are seeing in SOCs would not be possible. Hierarchy in particular allows the reuse of component blocks, such as CPU cores.… Read More

Surviving in the Age of Digitalization

There was an interesting keynote at DVCon last month. It was titled “Thriving in the Age of Digitalization” which introduced the concept of digital twins for design and production. It was presented by Fram Akiki who is a relative newcomer to EDA but has an interesting history so I will start there.

Fram and I got started in the semiconductor… Read More

Mentor Showcases Digital Twin Demo

Mentor put on a very interesting tutorial at DVCon this year. Commonly DVCon tutorials center around a single tool; less commonly (in my recent experience) they will detail a solution flow but still within the confines of chip or chip + software design. It is rare indeed to see presentations on a full system design including realistic… Read More

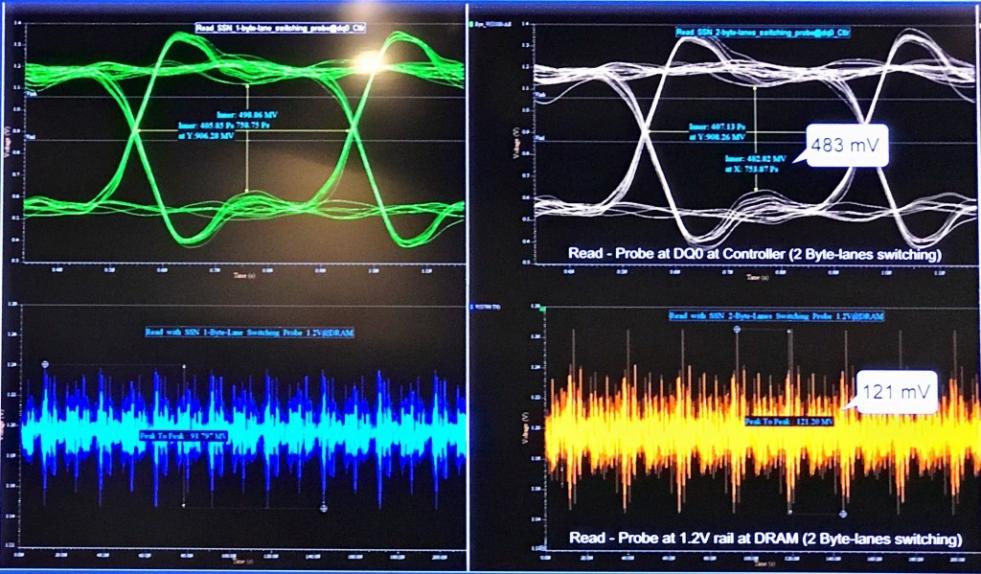

Mentor Automating Design Compliance with Power-Aware Simulation HyperLynx and Xpedition Flow

High-speed design requires addressing signal integrity (SI) and power integrity (PI) challenges. Power integrity has a frequency component. The Power Distribution Network (PDN) in designs has 2 different purposes: providing power to the chip, and acting as a power plane reference for transmission-line like propagating … Read More