RISC-V processor IP is abundant. Open-source code for RISC-V is also widely available, but typically project-based code solves one specific problem. Using only pieces of code, it’s often up to a development team integrate a complete application-ready stack for creating an embedded device. A commercial embedded software development… Read More

Using EM/IR Analysis for Efinix FPGAs

I’ve been following the EM/IR (Electro-Migration, IR is current and resistance) analysis market for many years now, and recently attended a presentation from Steven Chin, Sr. Director IC Engineering of Efinix, at the User2User event organized by Siemens EDA. The Tuesday presentation was in the morning at the Marriott… Read More

Methods for Current Density and Point-to-point Resistance Calculations

IC reliability is an issue that circuit design engineers and reliability engineers are concerned about, because physical effects like high Current Density (CD) in interconnect layers, or high point-to-point (P2P) resistance on device interconnect can impact reliability, timing or Electrostatic Discharge (ESD) robustness.… Read More

3D IC Update from User2User

Our smart phones, tablets, laptops and desktops are the most common consumer products with advanced 2.5D and 3D IC packaging techniques. I love seeing the product tear down articles to learn how advanced packaging techniques are being used, so at the User2User conference in Santa Clara I attended a presentation from Tarek Ramadan,… Read More

Joseph Sawicki of Siemens EDA at User2User

I attended the annual user group meeting called User2User in Santa Clara this year, hosted by Siemens EDA, with 51 presentations by customers in 11 tracks, and keynotes during each lunch hour from semiconductor executives. Joseph Sawicki, Executive VP, IC Segment, at Siemens EDA presented on a Tuesday, along with Prashant Varshney,… Read More

Cybersecurity Threat Detection and Mitigation

Every week in the technology trade press I am reading about cybersecurity attacks against web sites, apps, IoT devices, vehicles and even ICs. At the recent IP SoC Silicon Valley 2022 event in April I watched a cybersecurity presentation from Robert Rand, Solution Architect for Tessent Embedded Analytics at Siemens EDA. Common… Read More

Efficient Memory BIST Implementation

Test experts use the acronym BIST for Built In Self Test, it’s the test logic added to an IP block that speeds up the task of testing by creating stimulus and then looking at the output results. Memory IP is a popular category for SoC designers, as modern chips include multiple memory blocks for fast, local data and register storage… Read More

Designing a FinFET Test Chip for Radiation Threats

Much of the technology that goes into aerospace applications is some of the most advanced technology that exists. However, these same systems must also offer the highest level of reliability in what is arguably an extremely difficult environment. For semiconductors a major environmental risk in aerospace applications are … Read More

Path Based UPF Strategies Explained

The development of the Unified Power Format (UPF) was spurred on by the need for explicit ways to enable specification and verification of power management aspects of SoC designs. The origins of UPF date back to its first release in 2007. Prior to that several vendors had their own methods of specifying power management aspects … Read More

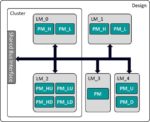

Co-Developing IP and SoC Bring Up Firmware with PSS

With ever challenging time to market requirements, co-developing IP and firmware is imperative for all system development projects. But that doesn’t make the task any easier. Depending on the complexity of the system being developed, the task gets tougher. For example, different pieces of IP may be the output of various teams… Read More