Often designers are amazed at the diversity of requirements fabricators and manufacturers have for metal filled areas in advanced package designs. Package fabricators and manufacturers do not like solid metal planes or large metal areas. Their strict metal fill requirements address two main issues. The dielectric and metal… Read More

Machine Learning in the Fab at #59DAC

It used to be true that a foundry or fab would create a set of DRC files, provide them to designers, and then the process yield would be acceptable, however if the foundry knows more details about the physical implementation of IC designs then they can improve the yield. Using a digital twin of the design, process and metrology steps… Read More

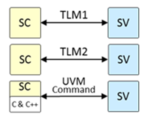

Connecting SystemC to SystemVerilog

Siemens EDA is clearly on a mission to help verifiers get more out of their tools and methodologies. Recently they published a white paper on UVM polymorphism. Now they have followed with a paper on using UVM Connect, re-introducing how to connect between SystemC and SystemVerilog. I’m often mystified by seemingly overlapping… Read More

Today’s SoC Design Verification and Validation Require Three Types of Hardware-Assisted Engines

Lauro Rizzatti offers Semiwiki readers a two-part series on why three kinds of hardware-assisted verification engines are now a must have for semiconductor designs continues today. His interview below with Juergen Jaeger, Prototyping Product Strategy Director in the Scalable Verification Solution division at Siemens EDA,… Read More

Resilient Supply Chains a Must for Electronic Systems

The last few years have seen multiple disruptions in the supply chain in many industries. One of the key technologies that many fingers have pointed to is the semiconductor technology. As products in all industries become more electronics based, semiconductors play a key role since no end system could function today without … Read More

Five Key Workflows For 3D IC Packaging Success

An earlier blog started with the topic of delivering 3D IC innovations faster. The blog covered the following foundational enablers for successful heterogeneous 3D IC implementation.

- System Co-Optimization (STCO) approach

- Transition from design-based to systems-based optimization

- Expanding the supply chain and tool

IC Layout Symmetry Challenges

Many types of designs, including analog designs, MEMs, and image sensors, require electrically matched configurations. This symmetry has a huge impact on the robustness of the design across process variations, and its performance. Having an electrically matched layout basically means having a symmetric layout. To check … Read More

Verifying 10+ Billion-Gate Designs Requires Distinct, Scalable Hardware Emulation Architecture

In a two-part series, Lauro Rizzatti examines why three kinds of hardware-assisted verification engines are a must have for today’s semiconductor designs. To do so, he interviewed Siemens EDA’s Vijay Chobisa and Juergen Jaeger to learn more about the Veloce hardware-assisted verification systems.

What follows is part one,… Read More

UVM Polymorphism is Your Friend

Rich Edelman of Siemens EDA recently released a paper on this topic. I’ve known Rich since our days together back in National Semi. And I’ve always been impressed by his ability to make a complex topic more understandable to us lesser mortals. He tackles a tough one in this paper – a complex concept (polymorphism) in a complex domain… Read More

Delivering 3D IC Innovations Faster

3D IC technology development started many years ago well before the slowing down of Moore’s law benefits became a topic of discussion. The technology was originally leveraged for stacking functional blocks with high-bandwidth buses between them. Memory manufacturers and other IDMs were the ones to typically leverage this … Read More