Chiplet is a hot topic in the semiconductor world these days. So much so that if one hasn’t heard that term, the person must be living on a very isolated islet. Humor aside, products built using chiplets-based methodology have been in existence for at least some years now. Companies such as Intel, AMD, Apple and others have integrated… Read More

Electronic Design Automation

SEMI ESD Alliance CEO Outlook Sponsored by Keysight Promises Industry Perspectives, Insights

Spring wouldn’t be the same without an opportunity to hear from some of the most visible executives of electronic system design (ESD) market segment. The in-person CEO Outlook sponsored by Keysight and hosted by the ESD Alliance, a SEMI Technology Community, will be held Thursday, May 18, in Santa Clara, Calif.

Attendees can expect… Read More

Takeaways from CadenceLIVE 2023

Given popular fascination it seems impossible these days to talk about anything other than AI. At CadenceLIVE, it was refreshing to be reminded that the foundational methods on which designs of any type remain and will always be dominated in all aspects of engineering by deep, precise, and scalable math, physics, computer science… Read More

Curvilinear Mask Patterning for Maximizing Lithography Capability

Masks have always been an essential part of the lithography process in the semiconductor industry. With the smallest printed features already being subwavelength for both DUV and EUV cases at the bleeding edge, mask patterns play a more crucial role than ever. Moreover, in the case of EUV lithography, throughput is a concern, … Read More

Tessent SSN Enables Significant Test Time Savings for SoC ATPG

SoC test challenges arise due to the complexity and diversity of the functional blocks integrated into the chip. As SoCs become more complex, it becomes increasingly difficult to access all of the functional blocks within the chip for testing. SoCs also can contain billions of transistors, making it extremely time-consuming… Read More

Chiplet Q&A with Henry Sheng of Synopsys

At the recent Synopsys Users Group Meeting (SNUG) I had the honor of leading a panel of experts on the topic of chiplets. One of those panelists was the very personable Dr. Henry Sheng, Group Director of R&D in the EDA Group at Synopsys. Henry currently leads engineering for 3DIC, advanced technology and visualization.

Are we

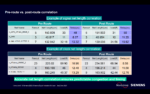

… Read MoreUsing ML for Statistical Circuit Verification

I’ve been following Solido as a start-up EDA vendor since 2005, then they were acquired by Siemens in 2017. At the recent User2User event there was a presentation by Kwonchil Kang, of Samsung Electronics on the topic, ML-enabled Statistical Circuit Verification Methodology using Solido. For high reliability circuits… Read More

Gate Resistance in IC design flow

MOSFET gate resistance is a very important parameter, determining many characteristics of MOSFETs and CMOS circuits, such as:

• Switching speed

• RC delay

• Fmax – maximum frequency of oscillations

• Gate (thermal) noise

• Series resistance and quality factor in MOS capacitors and varactors

• Switching speed and uniformity… Read More

Achieving Optimal PPA at Placement and Carrying it Through to Signoff

Performance, Power and Area (PPA) metrics are the driving force in the semiconductor market and impact all electronic products that are developed. PPA tradeoff decisions are not engineering decisions, but rather business decisions made by product companies as they decide to enter target end markets. As such, the sooner a company… Read More

Anirudh Keynote at Cadence Live

Anirudh is an engaging speaker with a passion for technology. Acknowledging the sign of the times, he sees significant value-add in AI but reminded us that it is a still supporting actor in system design and other applications where star roles will continue to be played by computational software that’s founded in hard science, … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry