At DAC on Wednesday Rick Stanton of Dassault Systems gave me an update on what’s new with DesignSync, a design data management tool offered since 1998. Rick and I both worked at Viewlogic in the 90’s along with Dennis Harmon who then founded Synchronicity, later acquired by Dassault Systems.… Read More

Electronic Design Automation

Webinar: how to reduce mobile device cost and board space with LLI

LLI Specification has been officially released by the MIPI Alliance, at the occasion of the Mobile World Congress in Barcelona, this year. As indicated by the name, the round-trip latency of the LLI inter-chip connection is fast enough for a mobile phone modem to share an application processor’s memory while maintaining… Read More

Designing a Wafer-Scale Image Sensor for use in X-Rays

At Intel we mused about designing wafer-scale integration (WSI) back in the 70’s however I just learned about how Dr.Renato Turchetta at the Science and Technology Facilities Council (STFC) designed a wafer-scale imaging sensor chip for X-Ray applications. I was also able to interview Dr. Turchetta to learn more about… Read More

EDA Tools to Optimize Memory Design

I met with Amit Gupta, President and CEO of Solido at DAC on Tuesday to get an update on their EDA tools used in the design of memory, standard cells and low-power. In 2012 they’ve expanded to add three new software packages: Memory, Standard Cell, Low Power. They must be doing something right because at DAC this year I see more… Read More

IC Cell Library Characterization at DAC

Edmond Macaluso, President of Z-Circuit Automation met with me at DAC on Tuesday afternoon to provide an overview of how their EDA tools characterize cell libraries. … Read More

Double Patterning Technology at DAC

David Abercrombie from Mentor Graphics met with me on Tuesday at DAC to provide an update on DPT – Double Patterning Technology, something new required for several layers starting at the 20nm node in order to get any IC yield. DPT is also part of Multiple-Patterning.… Read More

IPL Alliance at DAC

Lunch on Tuesday at DAC was sponsored by the IPL Alliance and thankfully this year they skipped the attempt at humor and focused on interoperable PDKs. Presenting companies include: Synopsys, Dongbu HiTek, TowerJazz, X-FAB and Si2. Having both OpenPDK and iPDK on the same platform does sound like a peaceful co-existence to me,… Read More

Atrenta Aquires NextOp

Atrenta announced today that it is acquiring NextOp Software. NextOp sells a tool BugScope that provides assertion synthesis technology. This complements Atrenta’s SpyGlass products for improving the process for design of complex semiconductor IP and SoCs.

I went to Atrenta’s office to talk to Ajoy Bose (CEO)… Read More

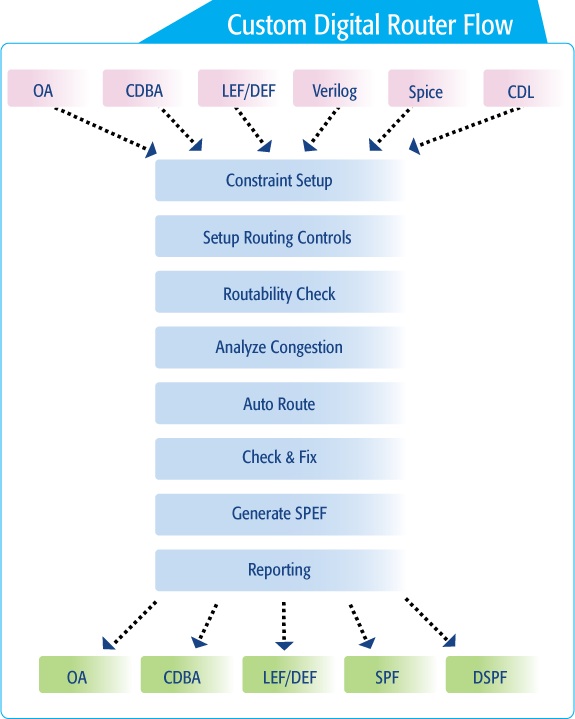

Shape-based IC Routing at DAC

IC place and route is a big challenge so we see many EDA companies creating tools. On Tuesday at DAC I met with Dave Noble of Pulsic to get an update.

Notes

Dave Noble, VP Operations (EDA since 2003), Sperry Univac since 1974

– had been an EDA distributor for Pulsic as well

More leads qualified on Monday than all days of last year … Read More

3D Thermal and Mechanical Stress for IC Packaging

3D has been a growing buzz word in IC design and packaging for several years now, so it’s refreshing to actually find an EDA vendor that has developed tools to help analyze something like 3D thermal and mechanical stress at DAC. … Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior