The next event in the Jim Hogan Emerging Companies series (organized by the EDAC Emerging Companies Committee) will be on 17th October at Cadence (I’m guessing in building 5 but I’m sure there will be signs). The specific topic this time will be How to Raise Money and How Not to Spend it. The evening will focus on different… Read More

Electronic Design Automation

17th Si2 Conference – October 9 – Santa Clara, CA

This conference will begin with a keynote address by my good friend Jim Hogan, EDA industry pioneer and venture capitalist. Jim has worked in the semiconductor design and manufacturing industry for more than 35 years and is very candid about his experience and vision for the future of EDA. This keynote and Q&A alone is worth … Read More

Verifying Finite State Machines

Finite state machines (FSMs) are a very convenient way of describing certain kinds of behavior. But like any other aspect of design, it is important to get everything right. Since finite state machines have been formally studied, there is a lot of knowledge about the types of bugs that a finite state machine might exhibit.

When flipflops… Read More

Built to last: LTSI, Yocto, and embedded Linux

The open source types say it all the time: open is better when it comes to operating systems. If you’re building something like a server or a phone, with either a flexible configuration or a limited lifetime, an open source operating system like Linux can put a project way ahead.

Linux has always started with a kernel distribution,… Read More

Custom IC and AMS Tool Flow with Synopsys

The big three EDA companies all have Custom IC and AMS tool flows as shown in the following comparison table:… Read More

Wiring Harness Design

In 2003 Mentor acquired a company doing wiring harness design. Being a semiconductor guy this wasn’t an area I’d had much to do with. But more than most semiconductor people I expect.

But back when I was an undergraduate, I had worked as a programmer for a subsidiary of Philips called Unicam that made a huge range of spectrometers… Read More

3D Memories

At DesignCon earlier this year, Tim Hollis of Micron gave an interesting presentation on 3D memories. For sure the first applications of true 3D chips are going to be stacks of memory die and memory on logic. The gains from high bandwidth access to the memory and the physically closer distance from memory to processor are huge.

Micron… Read More

A Brief History of Cadence Design Systems

EDA software for IC and system design became a commercial business in the early 1980s. In those days, 3 companies – Daisy Systems, Mentor Graphics, and Valid Logic Systems – dominated the emerging EDA industry. However, two small startups that emerged in the early 1980s grew rapidly and merged to form Cadence Design Systems in 1988.… Read More

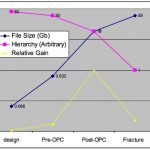

The Need for OASIS in Post-layout IC Databases

OASIS is a hierarchical IC file format used for IC designs that is gradually replacing GDS II throughout the mask data stages. The compelling reason for using OASIS has always been the reduction of file size, and speed up of processing times through the use of hierarchy and fewer translation steps.

At the 45nm node an actual M1 layer… Read More

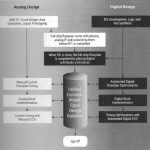

Mixed-Signal Methodology Guide

Last week I reviewed Chapter 1 in the new book: Mixed-Signal Methodology Guide, and today I finish up my review of Chapters 2 through 11. You can read the entire book chapter by chapter, or just jump directly to the chapters most related to your design role or project needs. With multiple authors I was impressed with the wide range of… Read More

Is Intel About to Take Flight?