You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4466

[filter] => raw

[cat_ID] => 157

[category_count] => 4466

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

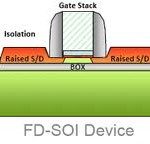

I recently spoke to Arvind Narayanan, Product Marketing Manager for Mentor’s place and route division about emerging technology. This of course led to FinFETS, FDSOI, performance, power, and cost-benefit. The battle between FDSOI and FinFETs, said Narayanan, is going to be something to watch.

Both FDSOI and FinFET technologies… Read More

RTL Restructuringby Daniel Payne on 04-04-2013 at 2:34 pmCategories: EDA

Hierarchical IC design has been around since the dawn of electronics, and every SoC design today will use hierarchy for both the physical and logical descriptions. During the physical implementation of an SoC you will likely run into EDA tool limits that require a re-structure of the hierarchy. This re-partitioning will cause… Read More

UBM’s EETimes and EDN today announced Kathryn Kranen as the lifetime achievement award winner for this years ACE awards program. Kathryn, of course, is the CEO of Jasper (and is also currently the chairman of EDAC). Past winners exemplify the prestige and significance of the award. Since 2005 the award was given to Gordon… Read More

I blogged last month about single event effects (SEE) where a semiconductor chip behaves incorrectly due to being hit by an ion or a neutron. Since we live on a radioactive planet and are bombarded by cosmic rays from space, this is a real problem, and it is getting worse at each process node. But just how big of a problem is it?

TFIT is … Read More

This year’s recipient of the Kaufman Award is Dr Chenming Hu. I can’t think of a more deserving recipient. He is the father of the FinFET transistor which is clearly the most revolutionary thing to come along in semiconductor for a long time. Of course he wasn’t working alone but he was the leader of the team at UC… Read More

Given the compressed time between 20nm and 16nm, twelve months versus the industry average twenty four months, it is time to start talking about 10nm, absolutely. Next Tuesday is the 19th annual TSMC Technology Symposium keynoted of course by the Chairman, Dr. Morris Chang.

Join the 2013 TSMC Technology Symposium. Get the latest… Read More

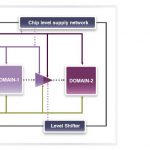

The burgeoning need of high density of electronic content on a single chip, thereby necessitating critical PPA (Power, Performance, Area) optimization, has pushed the technology node below 0.1 micron where static power becomes equally relevant as dynamic power. Moreover, multiple power rails run through the circuit at different… Read More

TSMC announced today that together with ARM they have taped out the first ARM Cortex-A57 64-bit processor on TSMC’s 16nm FinFET technology. The two companies cooperated in the implementation from RTL to tape-out over six months using ARM physical IP, TSMC memory macros, and a commercial 16nm FinFET tool chain enabled by… Read More

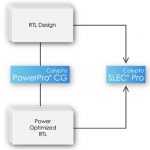

Sequential clock gating offers more power savings that can be obtained just with combinational clock gating. However, sequential clock gating is very complex as it involves temporal analysis over multiple clock cycles and examination of the stability, propagation, and observability of signal values.

Trying to do sequential… Read More

Ground. It’s that little downward-pointing triangle that somehow works miracles on every schematic. It looks very simple until one has to tackle modern power distribution network (PDN) design on a board with high speed and high power draw components, and you soon discover ground is a complicated fairy tale with a lot of influences.… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!