You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4439

[filter] => raw

[cat_ID] => 157

[category_count] => 4439

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

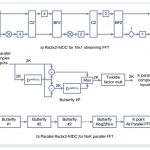

A basic building block of any communication system today is the fast Fourier transform, or FFT. A big advantage of FPGA implementations of FFTs is they can be scaled and tuned for the task at hand, optimizing data flow, resource use, and power consumption. Scaled, that is, up to the clock speed of the FPGA – or so it would seem.

Today’s… Read More

Going to Munich in May could be a very good idea, as it will give you the opportunity to listen to the keynote talk from Lip-Bu Tan. Who knows if you will learn in direct live the name of the next acquisition from Cadence in 2013, after Tensilica and Cosmic Circuits? In fact, there may not be new acquisition announcement, then this keynote… Read More

Mentor Graphics’ Best User2User Everby Beth Martin on 04-23-2013 at 5:45 pmCategories: EDA, Siemens EDA

Calling all Mentor users! Don’t forget to register for the U2U in San Jose on Thursday, April 25.

In addition to three worthy keynotes, you will find a more interactive and solution-focused day than in the past. There are sessions on place & route, custom/AMS, emulation, test and yield analysis, functional verification, Calibre… Read More

Forte Risesby Randy Smith on 04-23-2013 at 3:00 amCategories: EDA

Over the past few months there has been a bit of back-and-forth concerning the 2012 market data indicating that Forte Designs Systems had taken over the top spot (by revenue) in the high-level synthesis (HLS) market (see stories hereand here). Having worked in this segment for Synfora as VP of Marketing, and as a consultant to AutoESL,… Read More

If you are ever asked to organize a conference session do not hesitate, accept immediately and jump right in. When John Swan, EDPS General Chair, asked me to organize a day I hesitated. Fortunately he is not one to take no for an answer. It was an unforgettable experience on many levels and I hope to be involved with EDPS again next year.… Read More

I met Mike Sanie around DVCon time and planned to write a blog about the one year anniversary of Synopsys Discovery VIP which was announced during Aart’s keynote at DVCon in 2012. Eric covered it for SemiWiki here. But Synopsys had other stuff they wanted me to blog about and so it is a couple of months late. The 14th month anniversary… Read More

If there is a trend I can detect in verification in 2013, it is taking verification environments and making the user interface, scripts, and tools work uniformly across the whole spectrum of possible verification “substrates” from virtual platforms, FPGA boards, emulation, actual chips, RTL simulation and so … Read More

Methodics was founded in 2006 by 2 ex-Cadence experts in the Custom IC design tools space, Simon Butler and Fergus Slorach. They had a consulting company called IC Methods, active in Silicon Valley from 2000-2006, and when they needed to create a new company to service a consulting engagement that had turned into a product, they … Read More

Promoted by Accellera, SystemC User Groups are in work worldwide; NASCUGin North America, ESCUGin Europe and ISCUG in India. While I was shuffling between my day-to-day work and strategy management course/exams, I received an invitation from my long time colleague, President and CEO of Circuitsutra Technologies, Mr. Umesh… Read More

The 20th annual Electronic Design Process Symposium (EDPS) held April 18-19 at the Monterey Beach Hotel in Monterey California was an unqualified success. I know this because a bird (seagull?) sitting on the window sill of the conference room was so captivated by the fascinating insight provided by a number of luminaries that … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry