As I have mentioned before, Paul McLellan and I are writing a book on the history of the fabless semiconductor industry. There is a preview available HERE, it will initially be sold as an e-book on SemiWiki and put into print early next year. Working with Paul McLellan and Beth Martin on this was an amazing experience. The research,… Read More

Electronic Design Automation

Webinar: IP Lifecycle Management: What is it, what problems does it solve?

SoC’s are now dominated by IP blocks sourced either from 3rd parties or internal design teams. This means that IP is now critical to the success of the SoC, yet it is part of the design that teams have the least control over, or visibility into. Most design teams utilize at best ad-hoc methods to manage this IP, and the few that utilize… Read More

Using Formal to Find Bugs in ARM Microprocessors

2.5x ROI vs simulation. 25% of bugs found for only 10% of the overall verification cost. 36% of bugs in a current CPU project. These impressive results for formal analysis are what ARM’s Laurent Arditi reported at JUG 2013 after painstaking recording of metrics over several production programs.

As you can see from the above graph,… Read More

I could show you the FPGA, but then I’d have to configure you

One of the present ironies of the Internet of Things is as it seeks to connect every device on the planet, we are still designing those things with largely unconnected EDA tools. We may share libraries and source files on a server somewhere, but that is just the beginning of connection.

It is not surprising that synthesis tools from… Read More

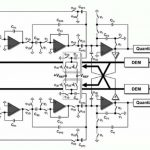

Device Noise Analysis of Switched-Cap Circuits

Switched-capacitor circuits are used in most CMOS mixed-signal ICs as:

- Track and hold circuits

- Integrators

- Operational Amplifiers

- Delta-sigma modulators

Delta-Sigma Modulator: IEEE J. Solid-State Circuits, vol. 43, no. 12, pp 2601-2612, Dec. 2008… Read More

M-PCIe, Data Converters, and USB 3.0 SSIC at IP SoC 2013

Synopsys is taking IP-SOC 2013 seriously, as the company will hold several presentations, starting with a Keynote: “Virtual Prototyping – A Reality Check”, by Johannes Stahl, Director, Product Marketing, System-Level Solutions, Synopsys, highlighting current industry practice around putting virtual prototyping to work… Read More

ARM in Samsung 14nm FinFET

I am at ARM TechCon today. One interesting presentation was made jointly between Samsung, Cadence and ARM themselves about developing physical libraries (ARM), a tool flow (Cadence) and test chips (Samsung). It was titled Samsung ARM and Cadence collaborate on the silicon-proven world first 14-nm FinFET Cortex-A7 ARM CPU and… Read More

ARC EM SEP Processor, Safety Ready Solution for Automotive

If you are familiar with Processor IP core, you certainly know DesignWare ARC EM4 core, 32-bit CPU that SoC designers can optimize for a wide range of uses, and differentiate by using patented configuration technology to tailor each ARC core instance to meet specific performance, power and area requirements. If you develop a product… Read More

Social Media at Mentor Graphics

You can often tell how important blogging and social media is to an EDA company by how much effort it takes to find their blog from the Home page. For the folks at Mentor Graphics I’d say that blogging is quite important, because it shows up as a top-level menu item. Notice also how important Twitter is, their latest tweets show… Read More

Correct by Construction Semiconductor IP

Semiconductor IP re-use enables modern SoC designs to be realized in a timely fashion, yet with hundreds of IP blocks in a chip the chances are higher that an error in any IP block could cause the entire system to fail. At advanced nodes like 28nm and smaller, the number of Process, Voltage and Temperature (PVT) corners is increasing… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center