You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4380

[filter] => raw

[cat_ID] => 157

[category_count] => 4380

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Formal approaches and security are a perfect match since you really want to prove that there are no holes in your security, rather than just being fairly confident. At the recent Jasper User Group meeting, Victor Purri presented some case studies in security verification.

The Jasper Security Path Verification (SPV) App is used… Read More

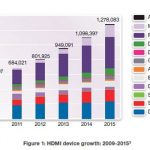

High Definition Multimedia Interface (HDMI) is today part of our day to day life, at home as well as at our office we are using devices integrating HDMI ports. HDMI penetration is well illustrated by this picture (created in Dec. 2011 by In-Stat): from DTV to Game console, the devices belong to the Consumer Electronics market segments,… Read More

Mentor is acquiring Oasys, subject to all the usual caveats about shareholder and regulatory approval. The shareholder paperwork went out earlier this week. The common stock is valueless so presumably the price is low (and Mentor historically has not paid high prices for its acquisitions).

So what is going to happen with the technology?… Read More

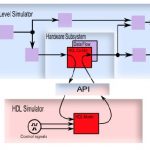

Our popular smart phones have a whole slew of RF-based radios in them for: Bluetooth, WiFi, LTE, GSM, NFC. Using just a single clock frequency for a DSP function or SoC is a thing of the past, so the design of multirate systems is here to stay. So now the challenge on the design and verification side is to use a methodology that supports:… Read More

AMD Goes 3Dby Paul McLellan on 12-13-2013 at 7:16 pmCategories: EDA

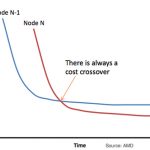

I attended the 3D packaging conference in Burlingame this week. The most interesting presentation to me was by Bryan Black of AMD. He argued very convincingly that Moore’s Law is basically over for the PC microprocessor business and the way forward is going to be 3D. AMD are clearly working on all this.

Increased density and… Read More

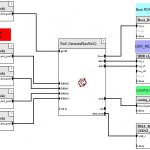

Interconnect plays a significant role in the semiconductor design of a SoC; if not architected and handled well, it can lead to an overdesigned SoC impacting on its power, performance and area. Since a SoC generally contains multiple IPs requiring different data paths to satisfy varying latency and performance cycles, it has … Read More

Jim Feldhan, President of Semico Research presented earlier this month at the Impact Conference on the topic: Focus on the IP Ecosystem. I’ve reviewed his 19 page presentation, and summarize it with:

- End markets like smart phones and tablets are dominant

- Growth drivers include the Internet of Things (IoT)

- World semi forecast

…

Read More

Donald Rumsfeld categorized what we knew into known unknowns and unknown unknowns. In a chip design, those unknown unknowns can bite you and leave you with a non-functional design, perhaps even intermittent failures which can be among the hardest problems to debug.

Chips are too big to do any sort of full gate-level simulation,… Read More

My very first thought when hearing about HSPICE is using it for IC simulation at the transistor-level, however it can also be used to simulate a package or PCB interconnect very accurately, like in the PCB layout of a DDR3 system where timing is critical. I attended a webinar this morning that was jointly presented by Zuken and Synopsys… Read More

Next year’s DVCon attendees can expect to learn about both practical solutions to their pressing problems that can be applied today and also receive a preview of the technologies that will affect them in the near future. DVCON is March 3-6, 2014 @ the DoubleTree Hotel in San Jose.

KEYNOTE: An Executive View of Trends and Technologies… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center