Gone are the days when analog design had its sweet space on a single chip. However, it’s the main driver in this new electronic world which is geared by Internet-of-Things, wireless, mobile, remote control and so on. How does an electronic device sense a touch by human, motion, temperature, sound etc.? It’s the analog circuitry … Read More

Electronic Design Automation

Mission Critical Role of Unmanned Systems – How to fulfill?

Do we ever imagine what kind of severe challenges mission critical unmanned systems in air, land and underwater face? They are limited in space and size; have to be light in weight, flexible in different types of operations and at the same time rugged enough to work in extreme climatic conditions. That’s not enough; amidst these … Read More

New Frontiers in Scan Diagnosis

As we move down into more and more advanced process nodes, the rules of how we test designs are having to change. One big challenge is the requirement to zoom in and fix problems by doing root cause analysis on test data alone, along with the rest of the design data such as detailed layout, optical proximity correction and so on. But without… Read More

Mastering the Magic of Multi-Patterning

I’ve been quite impressed that modern ICs use a lithography process with 193nm light sources to resolve final feature sizes at 20nm and smaller dimensions. We’ve been blogging about Double Patterning Technology (DPT) some 45 times in the past few years that enable 20nm fabrication, so one big question for me is, “How… Read More

2013 Awards, and the Winner is…Power

Of all the things that designers have to worry about in the power-performance-area (PPA) equation, the most challenging is power. SoCs have reached a point that we can put a lot of stuff on them, but if we are not careful we cannot light it all up at once. Dark silicon, where we put subsystems on a chip but then don’t have enough … Read More

ClioSoft at Arasan

Arasan recently adopted ClioSoft for data management (DM) for design and development of Arasan’s Silicon IP products. This morning I talked to Erik Peterson, Senior CAD and Verification Engineer AMS Design about their experiences bringing up ClioSoft.

Data management infrastructure is critical with engineering projects… Read More

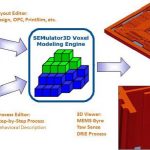

Quick MEMS Development Through Virtual Fabrication

The design and manufacture of MEMS is very different and in many ways more complex process than even the most advanced ICs. MEMS involve multiple degrees of freedom (i.e. the device to exhibit different characteristics under different physical state, motion or mechanics), making fabrication of MEMS extremely complex; and hence… Read More

2014: Keep calm, and program gates

I was tempted to call this piece “if you’re not using an FPGA, you’re doing it wrong,” but that didn’t quite capture the whole picture. Social memes aside, the FPGA as we know it is undergoing a serious transformation into a full blown SoC, and 2014 is the year that will usher in one of the biggest changes in the history of embedded design.… Read More

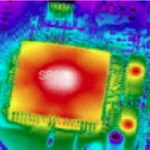

Early Thermal and Power Simulation Using Virtual Prototyping for Pedestrian Detection Applications

In the 1970’s we designed ICs first and when silicon came back then we measured the power and junction temperature. At that time there were no EDA simulation tools or models for full-chip power and temperature analysis. Fast forward to 2013 and we find that temperature and power are still demanding requirements for MPSoC … Read More

Macro Placement Challenges

One of the challenges of physical design of a modern SoC is that of macro placement. Back when a design just had a few macros then the flooplanning could be handled largely manually. But modern SoCs suffer from a number of problems. A new white paper from Mentor covers Olympus-SOCs features to address these issues:

- As we move to smaller

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center