The Internet of Things is on every technology mind these days, but what does it mean for the EDA community? Dennis Brophy of Mentor Graphics says the billions of things we are hearing about will not happen unless we find a way to build a lot more things, efficient things, and connected things. He has more thoughts in our recent interview.… Read More

Electronic Design Automation

Meeting the Challenges of Designing Internet of Things SoCs with the Right Design Flow and IP

Connecting “things” to the Internet and enabling sensing and remote control, data gathering, transmission, and analysis improves many areas: safety and quality of life, healthcare, manufacturing and service delivery, energy efficiency, and the environment. The concept of the Internet of Things (IoT) is quickly becoming… Read More

Design Methodology and its Impact on the Future of Electronics

Today at the Semisrael Expo 2013 (in Israel of course) Ajoy Bose gave a keynote on how design methodology will impact electronics. The big pictures is that microelectronics is driven by some major disruptive forces and, as a result, technology and industry are evolving dramatically, which creates a need for research and innovation… Read More

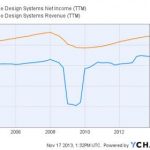

Cadence Design Systems’ Shares Are Surprisingly Cheap

In the third and final (for now) part of this series on the EDA design tool vendors, I’d like to take a closer look at Cadence Design Systems. This is probably the most interesting of the three from both an industry perspective as well as an investment perspective for a variety of reasons. With that said I’d like to first provide some … Read More

A Brief History of eSilicon

eSilicon Corporation was founded in 2000 with Jack Harding as the founding CEO and Seth Neiman of Crosspoint Venture Partners as the first venture investor and outside Board member. They both remain involved in the company today, with Jack continuing as CEO and Seth now serving as Chairman of the Board.

Both Harding and Neiman brought… Read More

Social Media at Synopsys

When I talk about social media and mention Synopsys you may quickly think of Karen Bartleson, the Senior Director of Community Marketing, because she:

- Blogs and podcasts

- Created the best interactive DAC game ever in 2013 using barcodes and points

- Tweets @karenbartleson

- Is president of the IEEE Standards Association

- Has over

TowerJazz and Silvaco BFF

Last week was the TowerJazz Technology Fair 2013. TowerJazz is the fourth biggest foundry in the world after TSMC, GF and UMC. They have fabs in Newport Beach (the old Jazz, itself with roots in Rockwell), two in Israel (the old Tower, with roots in National Semiconductor) and one in Japan (acquired from Micron). The technology fair… Read More

Signoff Summit: The Fastest Path to Design Signoff

Cadence’s Signoff Summit will be held next week, November 21 at Cadence in San Jose.

This is the first of a series of all-day Signoff Summits from Cadence that focus on the multiple facets of design signoff. This first summit will include keynote addresses plus sessions covering the multiple solution components that comprise… Read More

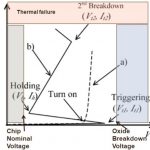

Full Chip ESD Sign-off – Necessary

As Moore’s law keeps going, semiconductor design density on a chip keeps increasing. The real concern today is that the shrinkage in technology node has rendered the small wire geometry and gate oxide thickness (although fine in all other perspectives) extremely vulnerable to ESD (Electrostatic Discharge) effects. More than… Read More

Bringing EDA to India

Why do all three big EDA companies have user group meetings in India? The answer is to grow the EDA market in India because so many multi-national companies have engineers in India doing SoC, and IP design work. In my 35 years of IC design and EDA experience I’ve had the pleasure of working with and knowing many engineers and managers… Read More

Quantum Computing Technologies and Challenges