The Seattle Seahawks had an awesome victory in the SuperBowl against the Denver Broncos, so folks living here in the Pacific Northwest are feeling proud and optimistic. The recent DesignConconference and exhibit ended 10 days ago and there were also victors announced in terms of the annual DesignVision awards that have three … Read More

Electronic Design Automation

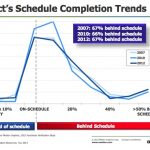

Verification Execution: When will we get it right?

Verification technologist Hemendra Talesaraattended a conference in Austin and asked me to post this article on verification execution for him as a blog. I first met Hemendra when he worked at XtremeEDA, and now he works at Synapse Design Automation – a design services company.

“In theory there is no difference between … Read More

Verification Execution: When will we get it right?

Verification technologist Hemendra Talesaraattended a conference in Austin and asked me to post this article on verification execution for him as a blog. I first met Hemendra when he worked at XtremeEDA, and now he works at Synapse Design Automation – a design services company.

“In theory there is no difference between … Read More

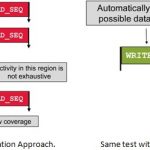

SoC Verification Closure Pushes New Paradigms

In the current decade of SoCs, semiconductor design size and complexity has grown by unprecedented scale in terms of gate density, number of IPs, memory blocks, analog and digital content and so on; and yet expected to increase further by many folds. Given that level of design, it’s imperative that SoC verification challenge has… Read More

Cadence Acquires Forte

Cadence today announced that it is acquiring Forte Design Systems. Forte was the earliest of the high-level synthesis (HLS) companies. There were earlier products. Synopsys had Behavioral Compiler and Cadence had a product whose name I forget (Visual Architect?), but both products were too early and were canceled. Cadence … Read More

Cliosoft Grows Again!

Cliosoft was one of the first companies to work with SemiWiki so they are an integral part of our amazing growth and we are part of theirs. I remember talking to Srinath Anantharaman (Cliosoft CEO) for the first time and discussing the goals of working together. It was simple really, there was disinformation in the market about Cliosoft… Read More

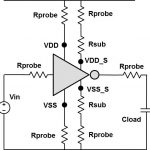

DesignCon 2014 AMS Panel Report

DesignCon 2014 was very crowded! I have not seen the attendance numbers but as the first conference of the New Year it was very encouraging. The strength of the fabless semiconductor ecosystem is collaboration and face-to-face interactions are the most valuable, absolutely.

The session I moderated was on Mixed Signal Design … Read More

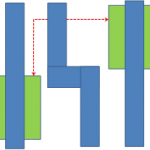

iDRM for Complex Layout Searches and IP Protection!

iDRM (integrated design rule manager) from Sage-DA is the world’s first and only design rule compiler. As such it is used to develop and capture design rules graphically, and can be used by non-programmers to quickly capture very complex and shape dependent design rules and immediately generate a check for them. The tool… Read More

CMOS Biosensor Breakthrough Enables Portable Diagnostics Solution

The panel I moderated at DesignCon last week was both entertaining and enlightining. One of the panelists, Zhimin Ding, is the CEO of an emerging fabless semiconductor company and here is their story:

In the past 5 to 10 years we have seen vast advancement in medical diagnostics technology. Doctors can now use DNA or anti-body analysis… Read More

Dual Advantage of Intelligent Power Integrity Analysis

Often it is considered safer to be pessimistic in estimating IR-drop to maintain power integrity of semiconductor designs; however that leads to the use of extra buffering and routing resources which may not be necessary. In modern high speed, high density SoCs having multiple blocks, memories, analog IPs with different functionalities… Read More

Solving the EDA tool fragmentation crisis