As the SoC design size, complexity and functionality keeps on increasing with multiple IPs packed together and design time and time-to-market keeps on decreasing amid critical constraints on PPA, there is no other alternative than to do the design first-time-right not to miss the window of opportunity. And that could be possible… Read More

Electronic Design Automation

Taiwan Trip Report: The Coming Simulation Crisis!

Even though the flight to Taiwan is somewhat difficult, I really do enjoy my trips to Hsinchu. In addition to the top two pure-play foundries being there, one of the top SoC companies (MediaTek) and many of the leading semiconductor design companies are there as well. All are a quick taxi ride from my home away from home, the Hotel Royal.… Read More

Expert Tool to View and Debug Design Issues at Spice Level

Spice view of a design, block or fragment of the design is probably the lowest level of functional description of a circuit in terms of transistors, resistors, capacitors, interconnect and so on, which in several ways acts as an ultimate proof of pudding for any semiconductor design before manufacturing. However, it’s generally… Read More

Transceiver Verification of a 20nm Altera FPGA Device

FPGA devices are a great way to drive silicon technology development because they contain both digital and analog IP, along with sophisticated IO cells. The highest performance IOs are transceivers, and Altera has recently designed the Arria 10 device family to include up to 96 transceivers, using a 20nm technology that can achieve… Read More

Smart Collaborative Design Reduces Business Risk

The semiconductor design industry is ever challenged with increasing chip density, manufacturing complexity with cutting-edge technologies, accommodating multiple IPs with different functionalities from various sources, optimizing power, performance and cost, maximizing manufacturability and reliability and still… Read More

A Comprehensive Power Analysis Solution for SoC+Package

Since power has become a critical factor in semiconductor chip design, the stress is towards decreasing supply voltage to reduce power consumption. However, the threshold voltage to switch devices cannot go down beyond a certain limit and these results in an extremely narrow margin for noise between the two. And that gets further… Read More

Design & EDA Collaboration Advances Mixed-Signal Verification through VCS AMS

Last week it was a rare opportunity for me to attend a webinar where an SoC design house, a leading IP provider and a leading EDA tool provider joined together to present on how the tool capabilities are being used for advanced mixed-signal simulation of large designs, faster with accuracy. It’s always been a struggle to combine design… Read More

EDA Plus ARM Equals Big Views!

In looking at the SemiWiki analytics, one of the top search terms that brings traffic to our site is ARM, just about anything ARM. In fact, that’s what the next SemiWiki book will be about. Yes, ARM is that interesting. While EDA is also one of our top search terms, EDA+ARM will get the most views, absolutely. And let’s face it, bloggers… Read More

SmartScan Addresses Test Challenges of SoCs

With advancement of semiconductor technologies, ever increasing sizes of SoCs bank on higher densities of design rather than giving any leeway towards increasing chip area and package sizes; a phenomenon often overlooked. The result is – larger designs with lesser number of pins bonded out of ever shrinking package sizes;… Read More

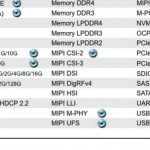

Synopsys VC VIP for Memory

Synopsys have been gradually broadening their portfolio of verification IP (VIP). It is 100% native SystemVerilog with native debug using Verdi (that was acquired from SpringSoft last year, now fully integrated into Verification Compiler). It has native performance with VCS. Going forward there are source code test suites.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center