Multiple clock domains in FPGAs have simplified some aspects of designs, allowing effective partitioning of logic. As FPGA architectures get more flexible in how clock domains, regions, or networks are available, the probability of signals crossing clock domains has gone way up.… Read More

Electronic Design Automation

Coverage Driven Verification for Analog?

We know there is a big divide between analog and digital design methodologies, level of automation, validation and verification processes, yet they cannot stay without each other because any complete system on a chip (SoC) demands them to be together. And therefore, there are different methodologies on the floor to combine analog… Read More

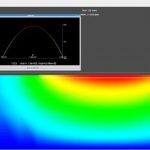

Electro-Thermal Simulation of Power Transistors

Power transistors are commonly used in applications like: hybrid vehicles, electric vehicles, automotive, home appliances, LED lighting, TVs, power and energy. In the old days an engineering team could build their device with power transistors, then after production run some thermal testing to see if they guessed the proper… Read More

Explaining HAPS-DX in an elevator

Every development team has been through this challenge: finding a tool that looks fantastic, then heading off to the manager one or two levels up who has enough signature authority for the purchase order. Signatures for amounts reading more than a couple of trailing zeros on POs are rarely free, or painless. … Read More

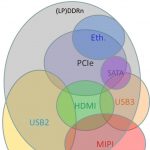

AMD Design IP Deal with Virage Logic… Oops… Synopsys

Whoever has said that history never repeats itself should read this recent PR from AMD! The news can be summarized in three points:

- Multi-year agreement gives AMD access to a range of Synopsys design IP including interface, memory compiler, logic library and analog IP for advanced FinFET process nodes

- Synopsys acquires rights

Samsung 14nm FinFET Design with Cadence Tools

The first consumer products with 20nm processing are arriving in 2014 like the 2 billion transistor A8 chip in the iPhone 6, however at the 14nm node there are new designs underway to continue the trend of Moore’s Law. To get a better feel for the challenges of designing with 14nm FinFET technology I watched a 23 minute video … Read More

Expansion at Calypto through Real Value Addition in SoC Design

When we get the notion of expansion of a company, it always provides a positive picture about something good happening to boost that expansion. There can be several reasons for expansion such as merger & acquisition, formation of joint venture or partnership, large customer orders and so on. However, organic expansion which… Read More

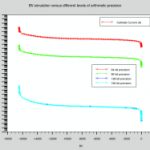

Is Number of Signoff Corners an Issue?

Semiconductor companies continue to use the traditional corner-based signoff approach that has been developed more than 40+ years ago and has since remained mainly unchanged as an industry paradigm. Initially it had 2 corners, namely Worst Case (WC) and Best Case (BC) with the maximum and minimum cell delay respectively. Note… Read More

TCAD to SPICE

Power devices have historically been made from silicon (Si), which has reached the limit of electric power loss reduction. With the superior physical and electrical properties of silicon carbide (SiC), we can expect to see a significant expansion in the amount of electric power conversion of electrical equipment as well as reduced… Read More

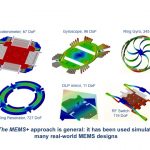

MEMS+, Bringing MEMS into the Electronic World

One of the things about MEMS devices is that they almost always live on a chip that also contains the electronics necessary to process the output from the sensor. For example, an on-chip accelerometer for a car airbag deployment will contain the electronics necessary to process the signal from the sensor and end up with something… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center