In a semiconductor design, keeping the design testable with high test coverage has always been a requirement. However with shrinking technology nodes and large, dense SoC designs and complex logic structures, while it has become mandatory to reach close to 100% test coverage, it’s extremely difficult to cope with the explosion… Read More

Electronic Design Automation

What Presentations to Attend During IP-SoC 2014 ?

Will you go to Grenoble next week to attend to IP-SoC? I will do it and will certainly listen to these Keynote Talks:

- “Platform IP: the next wave for SOCs from IoT to Datacenter” by Tony King-Smith, Executive Vice President, Marketing , Imagination Technologies

- “From Server-class to IoT SoCs: Enabling System

Noise & Reliability of FinFET Designs – Success Stories!

I think by now there has been good level of discussion on FinFET technology at sub-20 nm process nodes and this is an answer to ultra dense, high performance, low power, and billion+ gate SoC designs within the same area. However, it comes with some of the key challenges with respect to power, noise and reliability of the design. A FinFET… Read More

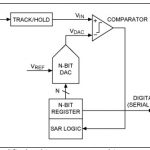

Debugging a 10 bit SAR ADC

SMIC (Semiconductor Manufacturing International Corporation) is a China-based foundry with technology ranging from 0.35 micron to 28 nm, and we’ve blogged about them before on SemiWiki. I’ve been reading about SMIC recently because they created a technical presentation for the MunEDA Technical Forum Shanghai… Read More

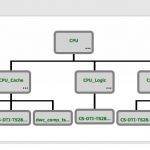

Effective Bug Tracking with IP Sub-systems

Designing an SoC sounds way more exciting than bug tracking, but let’s face it – any bug has the potential to make your silicon fail, so we need to take a serious look at the approaches to bug tracking. When using an IP or an IP subsystem in a design, the SoC integrators require some critical knowledge about this IP. The actual… Read More

Silvaco at the TSMC 2014 Open Innovation Platform

The success of our semiconductor eco-system depends on collaboration, so the annual TSMC OIP Event just held on September 30 at the San Jose Convention Center was a prime example of that. I didn’t attend this year, but I did follow up with Amit Nandaof Silvaco this week to hear about what they presented. As a consultant I’ve… Read More

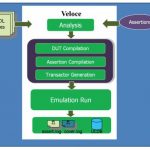

Improving Verification by Combining Emulation with ABV

Chip deadlines and the time to achieve sufficient verification coverage run continuously in a tight loop like a dog chasing its tail. Naturally it is exciting when innovative technologies can be combined so that verification can gain an advantage. Software based design simulators have been the mainstay of verification methodologies.… Read More

Adding a Digital Block to an Analog Design

My engineering background includes designing at the transistor-level, so I was drawn to attend a webinar today presented by Tanner EDAand Incentia about Adding a Digital Block to an Analog Design. Many of the 30,000 users of Tanner tools have been doing AMS designs, so adding logic synthesis and static timing analysis from Incentia… Read More

Cadence Mixed Signal Technology Forum

Yesterday was Cadence’s annual mixed-signal technology forum. I think that there was a definite theme running through many of the presentations, namely that wireless communication of one kind or another is on a sharp rise with more and more devices needing to connect to WiFi, Bluetooth and so on. This was most obvious during… Read More

Who Really Needs USB 3.1?

USB is certainly the most ubiquitous of the Interface protocols. I would bet that everybody is using USB everyday (I mean activate a USB connection, as we also use PCIe or SATA even if we don’t realize that we do it), but which application will get benefit of the 10 Gbps delivered by USB 3.1? Before precisely answering the question, … Read More

ASML High-NA EUV is Not Ready for High-Volume Production