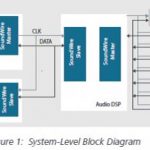

MIPI SoundWire specification will be integrated into mobiles systems, like smartphone or media tablet. In fact some of the well-known chip makers have already decided to integrate MIPI SoundWire into their last application processor release. MIPI SoundWire is also the type of specification which could be used in many other … Read More

Electronic Design Automation

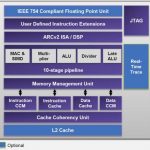

Linux and the ARC of the Coherent

Remember that thing called “real-time Linux”? Yeah, nobody else does either. As builds became configurable and clock speeds increased, embedded Linux manifested itself as fast enough for many applications – if a few other SoC details are addressed.

Most obvious for SoCs to run Linux is the need for a fully integrated MMU implementation.… Read More

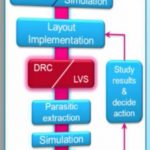

Finding Logic Issues Early that Impact Physical Implementation

Complex SoC project teams typically use a divide and conquer approach where specialized engineers work in separate domains, like front-end or back-end. The five major engineering tasks for IC design can be described as: RTL design, synthesis, floor planning, place and route, then finally design analysis.

What if you could detect… Read More

"How do I …?" Fast help for specific EDA software questions

It’s a question that we ask all the time. How do I replace a door? How do I set up a printer? For most questions in today’s world, you can open a browser, type a question into your favorite search engine…and voilà, there you go! Ten seconds of typing, a few more sorting through the results, and you have an answer (or many answers!). This … Read More

Mentor Wins v Synopsys

Just a couple of days ago I read a curious press release.Mentor Graphics Corp. (NASDAQ: MENT), today announced that a Portland, Oregon jury delivered a verdict in favor of Mentor in a trial in which Mentor asserted infringement of one of its patents against Emulation and Verification Engineering S.A. (EVE) and Synopsys, Inc. (Nasdaq:… Read More

EDA and the Nobel Prize in Physics!

What does EDA and the Nobel Prize for Physics have in common? Our very own Dr. Walden Rhines (CEO of Mentor Graphics):

The Nobel Prize in Physics 2014 was awarded jointly to Isamu Akasaki, Hiroshi Amano and Shuji Nakamura “for the invention of efficient blue light-emitting diodes which has enabled bright and energy-saving… Read More

How ST Designs with Layout Dependent Effects (LDE)

I first visited STat their Agrate, Italy site where Flash memory development is done. At DACthis year Antonio Bogani talked about how ST designs with LDE while using EDA tools and a PDK (Process Design Kit) from Cadence. They recorded the 17 minute presentation, and you can view it herewithout having to register. Antonio’s… Read More

EDAC Mixer, Kaufman and More. All Things EDAC

The next monthly EDAC mixer is next week on Thursday 23rd October from 6-8pm. It will be at the Sonoma Chicken Coop at 90 Skyport Drive in San Jose (right next to where Magma used to be and Atmel is). So come along and mingle with industry peers, all the the benefit of local charities. You don’t need to donate, just pay for your food… Read More

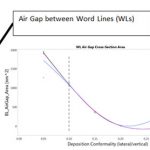

Proving the Power of Virtual Fabrication

There are many facets of our lives that are being driven to a more virtual method of doing things. This is largely due to issues such as scaling due to whatever reason – technical, business, economic. Let’s look at some general cases: In yesteryears people used to travel all the way for face-to-face meetings; today virtual meetings… Read More

TSMC ♥ Cadence!

One of the questions I routinely ask amongst the fabless semiconductor ecosystem is, “How are the EDA vendors doing?” There are always complaints because, let’s face it, we all like to complain. On occasion however I do hear about a vendor who goes above and beyond the call of duty and it really brightens my day.

Of late,… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?