About 3 years ago, I had written an article about consolidation in the semiconductor landscape where I had articulated 4 main reasons of consolidation – Macroeconomics, Business Leadership, Technology Leadership, and IP leadership. Back then, based on the state of affairs in the semiconductor industry, I had also mentioned… Read More

Electronic Design Automation

Talking Directly to EDA R&D

Many EDA companies keep their R&D engineers focused on product development and bug fixing, shielding them from any and all direct contact with end-users, mostly for fear of what might be revealed if such direct dialog were allowed. Customer support people are allowed to talk directly with customers, then pass along enhancement… Read More

Addressing Moore’s Law with the First Law of Real Estate: Location, location, location

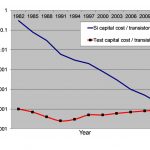

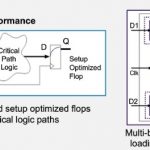

Design sizes and complexities have grown exponentially (it’s a Law!), and consequentially the task of silicon test has become proportionally more expensive. The cost of testing a device is proportional to the amount of test data that is applied, and therefore the time it takes, which in turn is proportional to both design size … Read More

SSD Storage Chips: Basic Interconnect Considerations

The joint development of 3D XPoint memory technology from Intel and Micron has once more brought the spotlight on data centers and chips for solid-state drives (SSDs). The two semiconductor industry giants claim that 3D XPoint memory is1,000 times faster than NAND Flash: the underlying memory content for SSDs. Such developments… Read More

I want to use USB Type C (and I want it now)

USB is certainly the most ubiquitous of the Interface protocols, used in our day to day life to connect multiple systems, as well as in professional segments like industrial or even high performance servers (yes, these systems integrates USB 3 connections). But USB is also one of the protocols able to generate frustration every… Read More

Silvaco 30 Years Ago

It’s Silvaco’s 30 year anniversary. You may already know the dry official story of the early days:

- Founded in 1984 by Dr Ivan Pesic

- In 1984 the initial product, Utmost, quickly became the industry standard for parameter extraction, device characterization and modeling.

- In 1985 Silvaco entered the SPICE circuit

Boost the Market for Interposer and 3D ICs with Assembly Design Kits

The traditional system-on-chip (SoC) design process has fully qualified verification methods embodied in the form of process design kits (PDKs). Why is it that chip design companies and assembly houses have no IC/package co-design sign-off verification process?

Package die are often produced using multiple processes and… Read More

Cadence 2015 Q2 Results

Let’s start by getting the financial stuff out of the way. Revenue was $416 million; non-GAAP operating margin was 28%; non-GAAP EPS was $0.27; and operating cash flow was $122 million (up at lot, it was just $47M in Q1 and $69M in Q2 of 2014).

The thing that the financial types are most interested in are the changes to Cadence’s… Read More

Build Low Power IoT Design with Foundation IP at 40nm

In a power hungry world of semiconductor devices, multiple ways are being devised to budget power from system to transistor level. The success of IoT (Internet of Things) Edge devices specifically depend on lowest power, lowest area, optimal performance, and lowest cost. These devices need to be highly energy efficient for sustained… Read More

Designing an IDCT for H.265 using High Level Synthesis

Math geeks know all about Inverse Discrete Cosine Transforms (IDCT) and a popular use is in the hardware architecture of High Efficiency Video Coding (HEVC), also known as H.265, the new video compression standard and widely used in consumer and industrial video devices. You could go about hand-coding RTL to create an IDCT function,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center