When I designed DRAM chips at Intel back in the 1970’s we didn’t really know what the die temperature would be before taping out silicon, instead we waited for packaged parts to come back and then did our thermal measurements. IC designers today don’t have that luxury of taping out their new SoC without having … Read More

Electronic Design Automation

Replacing the British Museum Algorithm

In principle, one way to address variation is to do simulations at lots of PVT corners. In practice, most of this simulation is wasted since it adds no new information, and even so, important corners will get missed. This is what Sifuei Ku of Microsemi calls the British Museum Algorithm. You walk everywhere. And if you don’t walk to… Read More

Moving up Verification to Scenario Driven Methodology

Verification complexity and volume has always been on the rise, taking significant amount of time, human, and compute resources. There are multiple techniques such as simulation, emulation, FPGA prototyping, formal verification, post-silicon testing, and so on which gain prominence in different situations and at different… Read More

What’s the Difference between Emulation and Prototyping?

Increasing system complexity requires constant focus on the optimal verification methodology. Verification environments incorporate a mix of: transaction-based stimulus and response monitors, (pseudo-)random testcase generation, and ultimately, system firmware and software. RTL statement and assertion coverage… Read More

Explore Your Interconnect the ICScape Way

One of the surprises at DAC for ICScape was to be listed on Gary Smith’s list of companies to see. Surprised, since ICScape had never presented their products to him. They were listed under design debug. They don’t have a single product that really falls under that description, but rather a family of tools under the ICExplorer… Read More

Congratulations Dr. Walden C. Rhines!

A funny thing happened at the Design Automation Conference last June in San Francisco. I was browsing the Kaufman award winner mug shots in the EDAC booth and noticed that Wally Rhines was NOT a winner. You can see them HERE. Immediately in disbelief I said to myself: Self, how can this be? Joe Costello, Aart de Geus, and some other guys… Read More

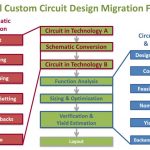

How MunEDA Helps Solve the Difficulties of AMS/RF IP Reuse

Reusing design IP is crucial for competitiveness. The need for reuse occurs with new designs on the same process node as the original design, new designs at the same node but using a different PDK or foundry, or designs on a different process node – usually smaller. However, achieving effective IP reuse has always been a challenge.… Read More

M&A Frenzy in the Chip Industry, the Growth of GaN, and Why It Matters

If expanding industries typically indicate vibrancy, a race to acquire and consolidate is generally reflective of the opposite – a period of slowed growth in mature, once high-flying categories. And while many industries experience a period of stardom, followed by a sharp and steady decline, we should be extremely worried when… Read More

Semiconductor Usage Revolves Around Asia

I just read Daniel Nenni’s blog titled “Is Silicon Valley Gridlock a Good Sign for Semiconductors?” Dan, there is no definitive answer to this, I mean in terms of semiconductors. Let me call it Semiconductor Gridlock in Silicon Valley. Yes it’s good because Silicon Valley promotes research, brings up innovative technology and… Read More

Improve SoC Front-end Design Productivity

I have been involved in SoC developments for a long time. During this period I tried to learn what impacts the productivity and subsequently the market opportunity. Over the last year or so at SoCScape I have been involved designing solutions that can improve them. I have decided to post some of my thoughts here in a series of blogs … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center