In the first part of this article, I talked about some of the key business aspects along with some technical aspects like system performance, functionality, and IP integration that drive the architecture of an SoC for its best optimization and realization in an economic sense. In this part, let’s dive into some more aspects that… Read More

Electronic Design Automation

Feed Your Mind and Body at 52nd DAC!

My beautiful wife and I attend the Design Automation Conference together whenever possible. More so now that she is the co-founder and CFO of SemiWiki. It is really nice for her to put a face to the invoices and personally thank our subscribers. Her first DAC was 1985 in Las Vegas. We were married for less than a year so it was like a second… Read More

Chip Design Problems Remain the Same, More or Less

For those who may not know me, here is a brief introduction. I started in the semiconductor business when RCA was still making vacuum tubes and I wrote EDA software before there was an EDA industry. I’ve designed and sold chips and developed, sold and used EDA tools at companies as big as General Electric and as small as seven people.… Read More

Calibre xACT Shakes Up 16nm and Below Extraction Game

Mentor Graphics made a big announcement regarding SOC extraction at their User2User conference in San Jose during April. Before I get to the meat of the announcement, I’d like to reflect back on the early days of Calibre-DRC at Mentor. I was in Sales at Mentor around 1999, and Calibre-DRC was the new kid on the block. We had to go convince… Read More

Ask me about Mentor at DAC!

If you’ve been following DAC general chair Anne Cirkel’s weekly blog, you know the conference program is now final. There’s much to suggest it will be a great DAC, including a record number of submissions in several content categories and a compelling lineup of keynoters. The week will start with an update on Google’s smart contact… Read More

SoC’s Shift Left Needs Software Integrity

Since Aart de Geus, co-CEO and co-founder of Synopsys, gave his keynote at the Synopsys User Group (SNUG) conference in Silicon Valley last March, I’ve been hearing a lot more about the “Shift Left” in semiconductor design. Although I couldn’t attend Synopsys’ 25[SUP]th[/SUP]SNUG, I found some short videos on the Synopsys website… Read More

MIPI CSI-2 and DSI IP? Better with FPGA Prototyping Set

Sourcing MIPI CSI-2 or DSI IP to a respected IP vendor is mandatory to build a peripheral IC or a SoC targeting mobile application as the chip maker simply can’t afford to do a re-spin because of Time-To-Market imperative. Buying this IP to a vendor also offering MIPI powered FPGA Prototyping Platforms is even better! Northwest Logic… Read More

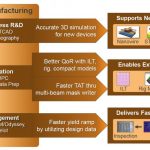

TCAD Enables Moore’s Law to Continue

We live in very interesting times, you can wear an Android watch from Samsung that uses 14 nm FinFET technology, attend the 52nd DAC conference in June to learn about EDA and IP vendors supporting FinFET, and read about research work for new devices down to 5 nm. TCAD is that critical software technology that enables the development… Read More

TSMC 10nm Readiness and 3DIC

At the TSMC Technology Symposium last month Suk Lee presented a lot of information on design enablement. Suk is an interesting guy with a unique background in ASIC, Semiconductor, EDA, and now Foundry. In baseball terms that would be like playing infield, outfield, home plate, and umpire!

Around the turn of the millennium Suk actually… Read More

Fractal at DAC 2015 – What’s new?

I have been observing Fractal Technologiesexhibiting at DACyear after year, and every year they have demonstrated good value added features in their tools for SoC and IP development. This year at 52[SUP]nd[/SUP] DAC Fractal’s booth number is 1110. Earlier in this year Fractal had added a new ‘Cdiff’ feature in its flagship product… Read More

Intel’s Pearl Harbor Moment