Process and device engineers are some of the unsung heroes in our semiconductor industry that have the daunting task of figuring out how to actually create a new process node that will fit some specific, market niche with sufficient yield to make their companies profitable and stand out from the competition. One such market segment… Read More

Electronic Design Automation

The Most Important Point You May Have Missed at CDNLive 2016!

This was the best keynote lineup I can remember at a user group meeting. All four speakers are visionaries but from very different perspectives. The video of the event will be up later this month but from my first count the word “System(s)” was mentioned 32 times and the underlying message will transform the semiconductor industry… Read More

Innovation in Transistor Design with Carbon Nanotubes

The New York Times article “IBM Scientists Find New Way to Shrink Transistors” by John Markoff focuses on the goal of the semiconductor industry to create smaller transistors in order to remain competitive while emphasizing cutting-edge design strategies with the use of carbon nanotubes. By switching from traditional methods… Read More

Analog Design Verification — Traceability is Required

Digital verification engineers have developed robust, thorough metrics for evaluating design coverage. Numerous tools are available to evaluate testbenches against RTL model descriptions — e.g., confirming that simulation regressions exhaustively exercise signal toggles, RTL statement lines, individual statement… Read More

Path FX – the Production Proven Answer to Static Timing Analysis with Variation

I want to compliment ChipGuy on a very nice write-up of a complex topic – how to model process variation in static timing.

… Read More

PCB Design Requires Both Speed and Accuracy of SI/PI Analysis

The prevailing industry trends are clear: (1) PCB and die package designs are becoming more complex, across both mobile and high-performance applications; (2) communication interface performance between chips (and their related protocols) is increasingly demanding to verify; (3) signal integrity and power integrity issues… Read More

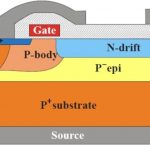

CMOS Radio Frequency Image Sensor Process

Image censoring with radio frequency (RF) in CMOS is a combination of light sensing chips and wireless communication. Typically, we were first engaged in the article, “RF Design Issues and Challenges in a CMOS Image Sensor Process”, because of the circuit design process required to make a functioning Radio Frequency transceiver.… Read More

Managing and Reusing IP in a Build-Borrow-Buy Era

Make-versus-buy inadequately describes what we do now in electronic systems design. We are on a continuum of design IP acquisition and use decisions, often with a portfolio of active projects and future projects depending on the outcome. Properly managing IP means adopting a build-borrow-buy mindset and tools capable of handling… Read More

IoT or Smart Everything?

I just attended a keynote presentation at SNUG from Aart de Geus, CEO of Synopsys. This event is well attended with some 2,500 people that are learning from the 96 presentations on all things Synopsys, semiconductor. IP, and foundry trends. There are big name sponsors like: GLOBALFOUNDRIES, Samsung, socioeconomic, TSMC, Fujitsu,… Read More

The Latest in Static Timing Analysis with Variation Modeling

In many ways, static timing analysis (STA) is more of an art than a science. Methodologists are faced with addressing complex phenomena that impact circuit delay — e.g., signal crosstalk, dynamic I*R supply voltage drop, temperature inversion, device aging effects, and especially (correlated and uncorrelated) process… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center