I first met John Durbetaki at Intel in Aloha, Oregon and we both had a keen interest in the nascent personal computer industry. My first PC was made by Radio Shack and dubbed the TRS-80 which maxed out at 48KB of RAM. I kept watch on Durbetaki as he left Intel and formed his own company OrCAD in 1985 to serve the needs of PC-based CAD software.… Read More

Electronic Design Automation

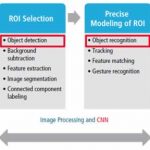

Cadence loads up on MACs for vision with CNNs

For vision DSP IP running convolutional neural networks (CNNs), a big driver of performance is increasing the bits processed per cycle with parallel MACs. Tom Simon did a great job in recent posts of introducing CNNs at a high level, so I’ll look at what is architecturally behind Cadence’s latest announcement: the Tensilica Vision… Read More

How to Deal With Seven Design Closure Issues

The challenge of tracking design progress is a shared problem for individual designers, team leaders, and project managers. At each level the ability to step back from just reviewing error log files and seeing the arc of the whole design as it moves forward is valuable. The difficulty of seeing the whole picture is exacerbated when… Read More

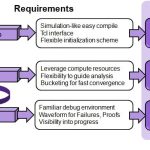

From Simulation to Emulation: 3 Steps to a Portable SystemVerilog/UVM Testbench

If your team is building large, complex designs that require millions of clock cycles to fully verify, you need both simulation and emulation.

Using emulation with simulation accelerates performance for dramatically reduced run times.… Read More

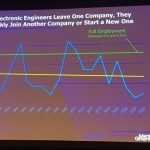

Are Layoffs Good for the Semiconductor Industry?

As I have mentioned before, semiconductor professionals are very smart people, pound for pound the smartest in the workforce in my opinion. So what happens when thousands of engineers from Qualcomm, Broadcom, Altera, and Intel get shown the door? They don’t go to work for Starbucks, they don’t go to the unemployment line, they … Read More

Ecosystem Partnership for Effective Network Hardware Design

When you’re designing a hardware solution to plug into what is arguably the most complex system of all – the Internet – you can’t get away with a little fake traffic to test whether your box is going to do all the right things at the right performance. You have to model realistic voice, video, data and wireless traffic in… Read More

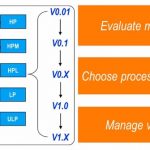

Process Development, CAD and Circuit Design

Working at Intel as a circuit designer I clearly remember how there were three distinct groups: Process Development, CAD and Circuit Design. Each of the groups sat in a different part of the building in Aloha Oregon, we had different job titles, different degrees, spoke with different acronyms and yet we all had to work together … Read More

Webinar alert – VHDL guru says its time to move up

Many years ago when I worked for Ed Staiano at Motorola, I learned never to use the word “comfortable” in a career context. I’m comfortable being with family and friends. This new high-back chair I sit in at my new faux-cocobolo desk (slightly distressed chalk-painted wood and industrial piping, awesome) is comfortable,… Read More

Software-Driven Verification Drives Tight Links between Emulation and Prototyping

I’ve mentioned many times what has become a very common theme in SoC and system verification – it has to be driven by the software because any concept of exhaustively verifying “everything” is neither feasible nor meaningful. Emulation has become a critical component of this flow in validating and regressing… Read More

Bringing Formal Verification into Mainstream

Formal verification can provide a large productivity gain in discovering, analyzing, and debugging complex problems buried deep in a design, which may be suspected but not clearly visible or identifiable by other verification methods. However, use of formal verification methods hasn’t been common due to its perceived complexity… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center