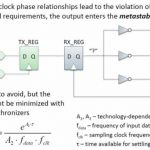

Many tools find clock domain crossings (CDCs) in FPGA designs. Some don’t find the right ones since they don’t comprehend things like in-house synchronizer constructs. Some find too many based on misunderstanding intent, inaccurate constraints, and other factors that lead to noise.… Read More

Electronic Design Automation

FREE Fabless: The Transformation of the Semiconductor Industry!

As most of you know SemiWiki published a book which is a really nice history of the fabless semiconductor ecosystem. Thousands of people have copies, we have received many compliments on it, and we are very proud. As a thank you to all SemiWiki members I would like to offer a free electronic version of the book (PDF). You can access it… Read More

Emulation as a Multi-User Shareable Resource

One of the great advantages of emulation is that runtimes are much faster than for simulation – sufficiently fast that you can really debug hardware together with software for comprehensive use-case testing. A not so great aspect is that emulators are expensive and, until relatively recently, not particularly easy to share across… Read More

Market Trends Motivate a Shift-Left in Functional Verification

Today, in the context of functional verification, industry trends are based on the needs of prominent vertical markets. There is some overlap in what these markets need, but there are some use models that are very specific to each market.

We assert this because we have a lot of customers asking about emulation solutions not from … Read More

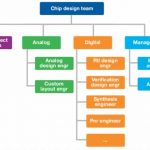

Organizing Data is First Step in Managing AMS Designs

Efficient collaboration is essential to meeting tight chip design schedules. In analog and mixed signal (AMS) design, collaboration has many facets. Design tools are usually specific to roles, and handoffs are numerous, especially when moving a design to a foundry. … Read More

Mentor Functional Verification Study 2016

Periodically, Mentor commissions a user/usage survey on Functional Verification, conducted by the Wilson Research Group, then they publish the results to all of us, an act of industry good-citizenship for which I think we owe them a round of thanks. Harry Foster at Mentor is breaking down the report into a series of 15 blogs. He’s… Read More

Requirements Management and IP Management Working Together

I first heard about requirements management back in 1995 while marketing a graphic HDL entry tool for an EDA vendor, and it sounded like a very useful automation approach, however our team quickly discovered that there were too many different vendors for requirements management, so there could be no simple way to integrate with… Read More

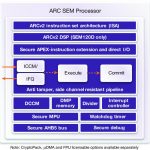

A Powerful Case for the ARC SEM Processor

Building devices for the IoT has become especially challenging thanks to two conflicting requirements. The device has to be small and ultra-low power in most applications but also in many of those applications it has to provide a high-level of security, especially to defend high-value targets like smart metering, payment terminals,… Read More

TSMC and Solido to Share Experiences with Managing Variation in Webinar

TSMC knows better than anyone the effect that variation can have at advanced process nodes. Particularly in memory designs and in standard cell designs, variation has become a very critical because of its effects on yield and because of the high-cost of compensating for it. Smaller feature sizes combined with lower voltage thresholds… Read More

Power-Aware Debug to Find Low-Power Simulation Bugs

When I worked at Intel designing custom chips my management would often ask me, “Will first silicon work?” My typical response was, “Yes, but only for the functions that we could afford to simulate before tape-out.” This snarky response would always cause a look of alarm, quickly followed by a second … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center