There’s always a lot of activity in EDA to innovate and refine specialized algorithms in functional modeling, implementation, verification and many other aspects of design automation. But when Google, Facebook, Amazon, IBM and Microsoft are pushing AI, deep learning, Big Data and cloud technologies, it can be hard not to see… Read More

Electronic Design Automation

Case study illustrates 171x speed up using SCE-MI

As SoC design size and complexity increases, simulation alone falls farther and farther behind, even with massive cloud farms of compute resources. Hardware acceleration of simulation is becoming a must-have for many teams, but means more than just providing emulation… Read More

Drift is a Bad Thing for SPICE Circuit Simulators

My first job out of college was with Intel, located in Aloha, Oregon and I did circuit simulations using a proprietary SPICE circuit simulator called ASPEC that was maintained in-house. While doing some circuit simulations one day I noticed that an internal node in one of my circuits was gradually getting higher and higher, even… Read More

Processors, Processors, Processors Everywhere

At first glance a processor conference might seem a bit arcane, however we live in an era where processors are ubiquitous. There is hardly any aspect of our lives that they do not touch in some way. Last week at the Linley Processor Conference the topics included deep learning, autonomous driving, energy, manufacturing, smart cities,… Read More

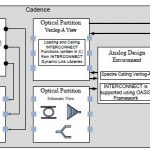

You’re Going to Want to Attend the Cadence Photonics Summit Workshop, October 19-20

Photonics IC’s (PIC’s) are used to transmit and receive data through a (single-mode or multi-mode) optical fiber carrier, and provide the requisite electro-optical conversion for system integration. The architecture of the PIC spans the full characteristics of data transmission and reception:

- light generation

Typically,… Read More

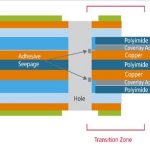

"Rigid-Flex Design is Coming"

Printed circuit boards that incorporate a combination of traditional PCB technology with flexible substrates, aka rigid-flex designs, have enabled an increasing variety of product designs, that leverage the unique physical form factor and lightweight options that rigid-flex technology offers. Yet, this technology requires… Read More

Meet the POWER9 Chip Family

When you looked at a chip in the past you primarily were concerned with two things: the speed of the chip, usually expressed in GHz, and how much power it consumed. Today the IBM engineers preparing the newest POWER chip, the 14nm POWER9, are tweaking the chips for the different workloads it might run, such as cognitive or cloud, and… Read More

Low power physical design in the age of FinFETs

Low power is now a goal for most digital circuit designs. This is to reduce costs for packaging, cooling, and electricity; to increase battery life; and to improve performance without overheating. I talked to the experts on physical design for ultra-low power at Mentor Graphics recently about the challenges to P&R tools and… Read More

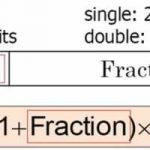

Cadence DSPs float for efficiency in complex apps

Floating-point computation has been a staple of mainframe, minicomputer, supercomputer, workstation, and PC platforms for decades. Almost all modern microprocessor IP supports the IEEE 754 floating-point standard. Embedded design, for reasons of power and area and thereby cost, often eschews floating-point hardware… Read More

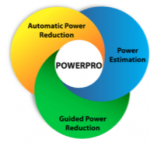

Power Exploration at RTL Design with Mentor PowerPro

There was a comment recently that design for low power is not an event, it’s a process; that comment is absolutely correct. Power is affected by everything in the electronic ecosystem, from application software all the way down to layout and process choices. Yet power as a metric is much more challenging to model and control than … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center