To paraphrase an Austen line, it is a truth universally acknowledged that implementation, power intent and design hierarchy don’t always align very well. Hierarchy is an artifact of legacy structure, reuse and division of labor, perhaps well-structured piecewise for other designs but not necessarily so for the design you now… Read More

Electronic Design Automation

AI Being Used from Probing to Simulation

The 54th annual DAC event is fast approaching, so I hope to see many of you in Austin on June 18-21. The phrases Machine Learning and AI are growing in all areas of software, so I’m glad to see it appearing in more EDA tool offerings over the past year or so. One company that I plan to visit at DAC is Platform Design Automation because… Read More

ClioSoft & DAC : Booth 613 – Collaborative Design, Design Data & IP Management and Design Reuse

It’s time again to gather for the next Design Automation Conference (DAC). This will be the 54[SUP]th[/SUP] such meeting and this year it runs from June 19[SUP]th[/SUP] – 21[SUP]st[/SUP] in the Live Music Capital of the World, Austin Texas. Put on your best duds, boots and cowboy hat and make your way to Texas.

While you are there … Read More

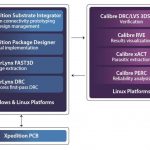

Tools for Advanced Packaging Design Follow Moore’s Law, Too!

There is an emerging set of advanced packaging technologies that enables unique product designs, with the capability to integrate multiple die, from potentially heterogeneous technologies. These “system-in-package” (SiP) offerings provide architects with the opportunity to optimize product performance, power, cost,… Read More

An InFormal Chat

Any sufficiently advanced technology is indistinguishable from magic, as the saying goes. Which is all very well when the purpose is entertainment or serving the arcane skills of a select priesthood, but it’s not a good way to grow a market. Then you want to dispel the magic aura, make the basic mechanics more accessible to a wider… Read More

Margin Call

A year ago, I wrote about Ansys’ intro of Big Data methods into the world of power integrity analysis. The motivation behind this advance was introduced in another blog, questioning how far margin-based approaches to complex multi-dimensional analyses could go. An accurate analysis of power integrity in a complex chip should… Read More

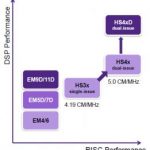

Is ARC HS4xD Family More a CPU or DSP IP Core?

When I had to define the various IP categories (processor, analog & mixed-signal, wired interfaces, etc.) to build the Design IP Report, I scratched my head for a while about the processor main category: how to define the sub-categories? Not that long ago, it was easy to identify a CPU IP core and a DSP IP core. As of today, if a DSP… Read More

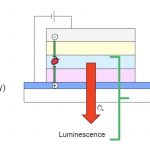

TCAD for TFT, LCD and OLED Displays

As I write there are multiple displays in front of me that use TFT, LCD or OLED displays:

- ViewSonic Monitors with 24″ display

- MacBook Pro with 15″ display

- iPad Air

- Samsung Galaxy Note 4

- Nexus 7 tablet

- Garmin Edge 820

Getting to IP Functional Signoff

In the early days of IP reuse and platform-based design there was a widely-shared vision of in-house IP development teams churning out libraries of reusable IP, which could then be leveraged in many different SoC applications. This vision was enthusiastically pursued for a while; this is what drove reusability standards and … Read More

RTL Correct by Construction

Themes in EDA come in waves and a popular theme from time to time is RTL signoff. That’s a tricky concept; you can’t signoff RTL in the sense of never having to go back and change the RTL. But the intent is still valuable – to get the top-level or subsystem-level RTL as well tested as possible, together with collateral data (SDC, UPF, etc)… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center