It was only back in May of this year that ClioSoft first introduced designHUB, a revolutionary new product that is meant to enable better use of intellectual property (IP) within a company. I wrote a SemiWiki article at the time of the announcement and mentioned it again in a lead-up article to the 54[SUP]th[/SUP] Design Automation… Read More

Electronic Design Automation

Cloud-Based Emulation

At the risk of attracting contempt from terminology purists, I think most of us would agree that emulation is a great way to prototype a hardware design before you commit to building, especially when you need to test system software together with that prototype. But setting up your own emulation resource isn’t for everyone. The … Read More

ARM and Cadence IP Simplify IoT System Design and Verification

As the Internet-of-Things (IoT) markets mature, we are seeing the complexity of IoT systems evolve from simple routing functions that connect IoT edge devices to the cloud into more complex system of systems that manage the interaction between multiple sensor-hubs. IoT sensor-hubs and gateways not only take care of basic care… Read More

Synopsys Opens up on Emulation

Synopsys hosted a lunch panel on Tuesday of DAC this year, in which verification leaders from Intel, Qualcomm, Wave Computing, NXP and AMD talked about how they are using Synopsys verification technologies. Panelists covered multiple domains but the big takeaway for me was their full-throated endorsement of the ZeBu emulation… Read More

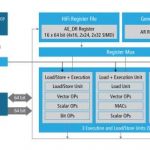

Tensilica HiFi 3z DSP Core: Leading Energy Efficiency

Tensilica HiFi DSP family, dedicated to voice and audio processing, is shipping over 1 billion units worldwide annually, thanks to the 75+ licensees. The new HiFi 3z architecture offers more than 1.3X better voice and audio processing performance than its predecessor, the HiFi 3 DSP, which leads the industry in the number of audio… Read More

A Functional Safety Primer for FPGA – and the Rest of Us

Once in a while I come across a vendor-developed webinar which is so generally useful it deserves to be shared beyond the confines of sponsored sites. I don’t consider this spamming – if you choose you can ignore the vendor-specific part of the webinar and still derive significant value from the rest. In this instance, the topic is… Read More

Emulation makes the What to See List

The analysts at Gary Smith EDA produce an annual What To See List for DAC and I quickly noticed that all three major EDA vendors were included on the list for the specific category of emulation. The big problem that emulation addresses is the ability to run in hardware an early version of your SoC so that software developers can get access… Read More

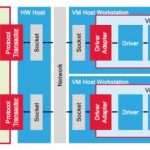

Virtualizing ICE

The defining characteristic of In-Circuit-Emulation (ICE) has been that the emulator is connected to real circuitry – a storage device perhaps, and PCIe or Ethernet interfaces. The advantage is that you can test your emulated model against real traffic and responses, rather than an interface model which may not fully capture… Read More

The Transformation of Silvaco!

Founded in 1984, Silvaco is now the largest privately held EDA company with a rich history including a recent transformation that is worth a blog if not a book. Coincidently, I started my career in Silicon Valley in 1984 and have had many dealings with Silvaco over the years including a personal relationship with Silvaco founder … Read More

Webinar: Ansys on Multi-Physics PDN Optimization for 16/7nm

On the off-chance you missed my previous pieces on this topic, at these dimensions conventional margin-based analysis becomes unreasonably pessimistic and it is necessary to analyze multiple dimensions together. People who build aircraft engines, turbines and other complex systems have known this for quite a long time. You… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center