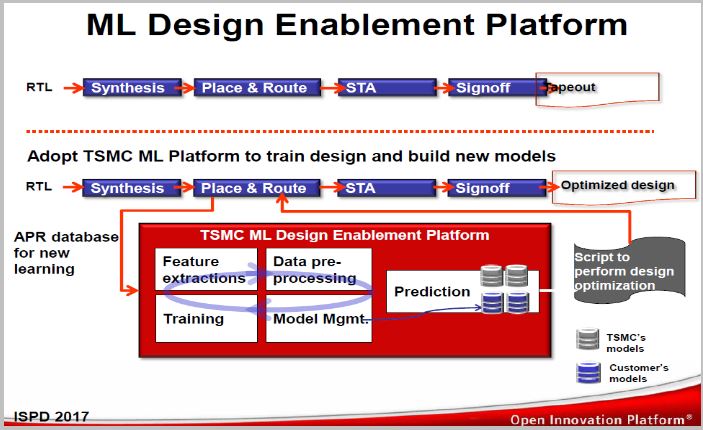

Recently we have been swamped by news of Artificial Intelligence applications in hardware and software by the increased adoption of Machine Learning (ML) and the shift of electronic industry towards IoT and automobiles. While plenty of discussions have covered the progress of embedded intelligence in product roll-outs, an… Read More

Electronic Design Automation

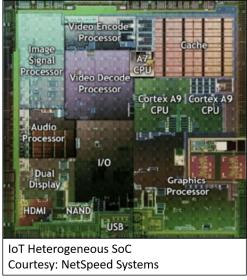

Effective Project Management of IoT Designs

ClioSoft is well known for their SoC design data management software SOS7 and more recently for their IP reuse ecosystem called designHUB. What is less known is how designHUB enables design teams to collaborate efficiently and better manage their projects by keeping everyone in sync during development. Not only does it provide… Read More

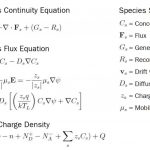

Using a TCAD Tool to simulate Electrochemistry

In college I took courses in physics, calculus, chemistry and electronics on my way to earn a BSEE degree, then did an 8 year stint as a circuit designer, working at the transistor level and interacting with fab and test engineers. My next adventure was working at EDA companies in a variety of roles. As a circuit designer I knew that … Read More

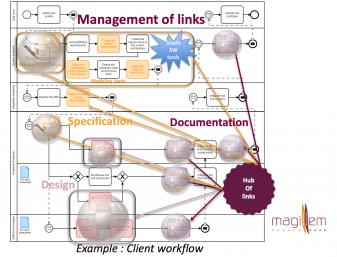

Design Data Intelligence

We have an urge to categorize companies, and when our limited perspective is of a company that helps with design, we categorize it as an EDA company. That was my view of Magillem, but I have commented before that my view is changing. I’m now more inclined to see them more as the design equivalent of a business intelligence organization… Read More

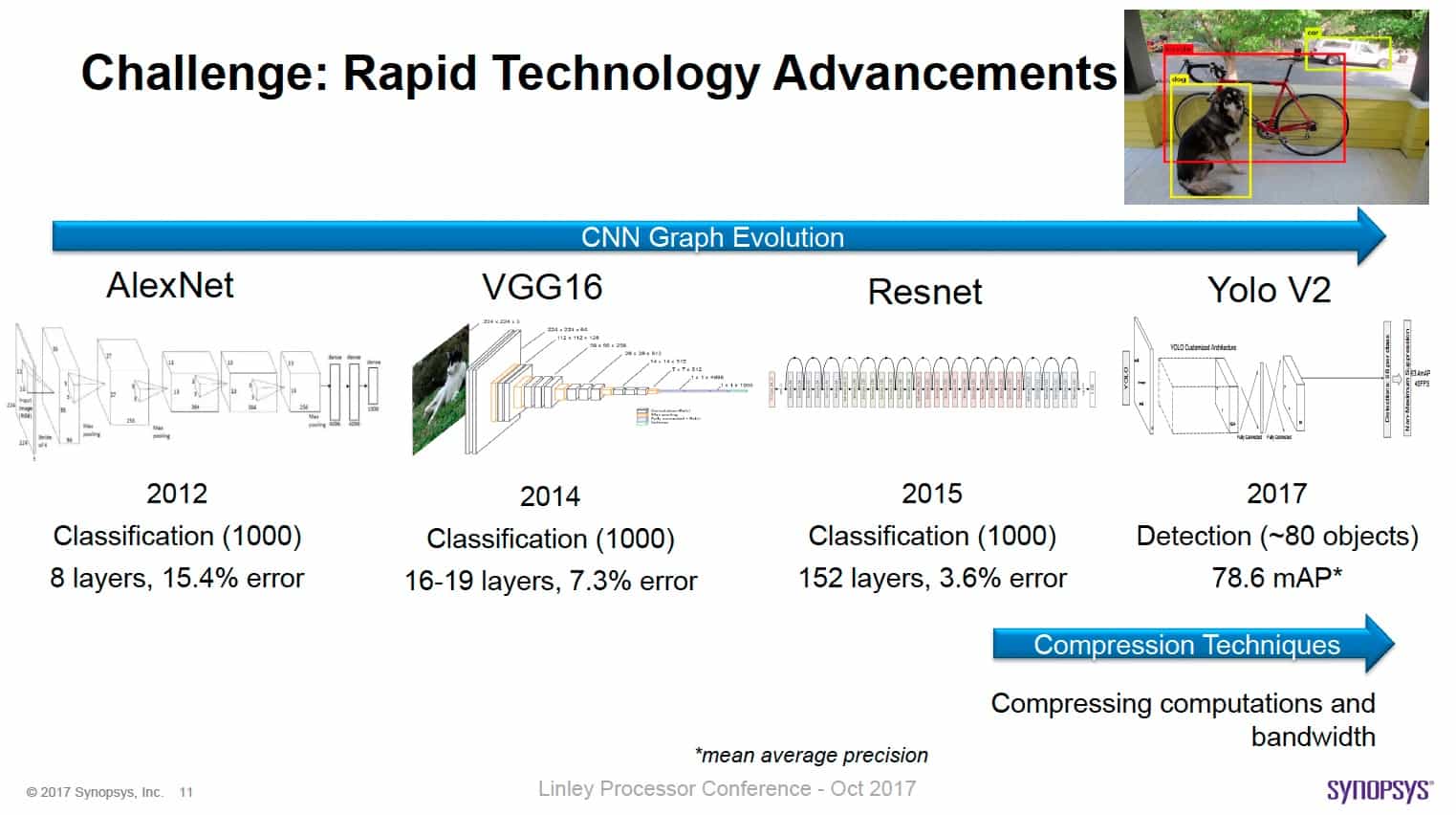

Synopsys discusses the challenges of embedded vision processing

Before the advent of convolutional neural networks (CNN), image processing was done with algorithms like HOG, SIFT and SURF. This kind of work was frequently done in data centers and server farms. To facilitate mobile and embedded processing a new class of processors was developed – the vision processor. In addition to doing a … Read More

Electronic Design for Self-Driving Cars Center-Stage at DVCon India

The fourth installment of DVCon India took place in Bangalore, September 14-15. As customary, it was hosted in the Leela Palace, a luxurious and tranquil resort in the center of Bangalore, and an excellent venue to host the popular event.

As reported in my previous DVCon India trip reports, the daily and evening traffic in Bangalore… Read More

1st Annual International Conference, Semiconductors ISO 26262

When we talk about the promise of ADAS and autonomous cars then along the way we also hear about this functional safety standard called ISO 26262 which semiconductor companies all pay close attention to. I recently learned about a new conference called Semiconductors ISO 26262, scheduled for December 5-7 in Munich, Germany. The… Read More

Good Library Hygiene Takes More Than an Occasional Scrub

You don’t shower only before you have to go to an important meeting (teenagers excepted). Surgical teams go further, demanding a strict regimen of hygiene be followed before anyone is allowed into an operating room. Yet we tend to assume that libraries and physical IP (analog, memories, other physical blocks) are checked and pronounced… Read More

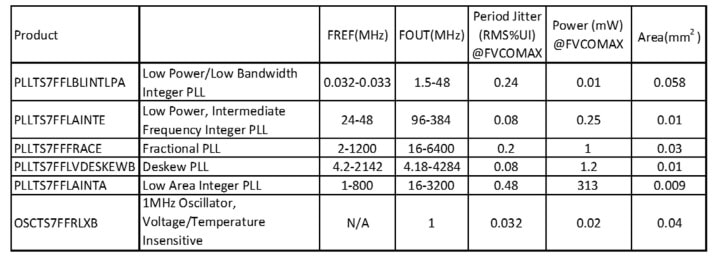

Silicon Creations talks about 7nm IP Verification for AMS Circuits

Designing at 7nm is a big deal because of the costs to make masks and then produce silicon that yields at an acceptable level, and Silicon Creations is one company that has the experience in designing AMS IP like: PLL, Serializer-Deserializer, IOs, Oscillators. Why design at 7nm? Lots of reasons – lower power, higher speeds,… Read More

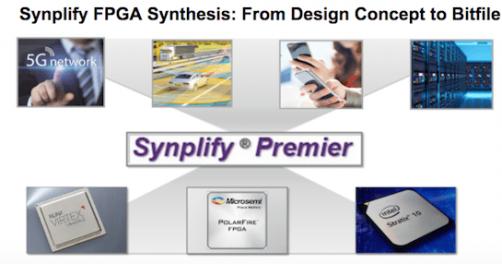

Webinar: Optimizing QoR for FPGA Design

You might wonder why, in FPGA design, you would go beyond simply using the design tools provided by the FPGA vendor (e.g. Xilinx, Intel/Altera and Microsemi). After all, they know their hardware platform better than anyone else, and they’re pretty good at design software too. But there’s one thing none of these providers want to… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center