Automotive applications are one of the hottest domains today in semiconductor design. We’re bombarded daily with articles on new hybrids, electric cars, ADAS and autonomous cars, trucks and busses. All of these applications are certainly amazing, but the devices that make them work still have to deal with the same old challenges,… Read More

Electronic Design Automation

Synopsys White Paper on IoT Security – Introduces DesignWare Root-of-Trust Module

As the internet of things (IoT) continues its climb to a trillion devices, there has been many articles and books written on the need for securing those devices. With all the IoT gear that I seem to be picking up as Christmas presents, I feel like I’m doing my part to help the market get there, but I have to say, I sure hope the SoC designers… Read More

When Invaluable Kills Business

Productivity is notoriously hard to sell. I recently visited a company where the engineering team wanted to evaluate one of our FPGA debug and analysis products on an existing board. This board had an FPGA that we supported and had all the required connectivity – it could just be used ‘out of the box’. Our tool – Exostiv… Read More

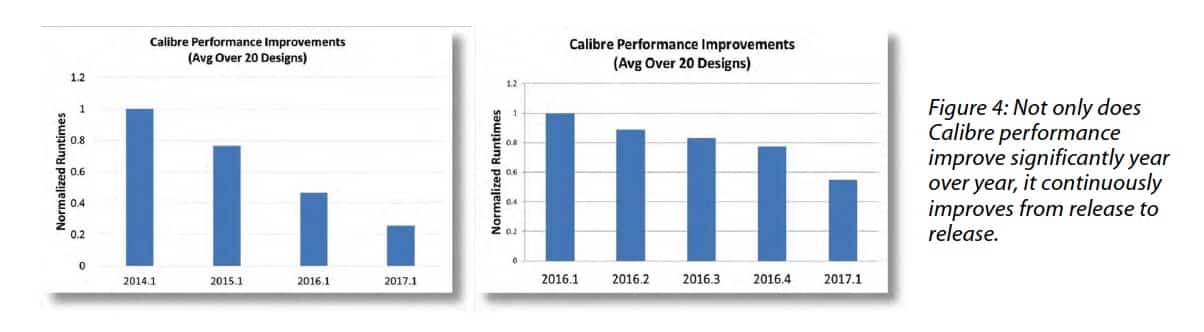

High Calibre Development Keeps Mentor on Top of the Game

One might be tempted to think that technology driven gains in computer performance might be enough to keep up with the needs of design and verification tools. We know that design complexity is increasing at a rate predicted by Moore’s Law. We also know that the performance of the computers used during IC development benefit from … Read More

Optimizing Return from your IP Portfolio

Given that SoC design today is predicated on IP reuse, you would assume that processes to deliver, maintain and communicate status on reusable IP should be highly optimized. But that’s not necessarily the case, especially when so many design companies have consolidated, each brings its own IP libraries, design flows, license… Read More

Blurring Boundaries

I think most of us have come to terms with the need for multiple verification platforms, from virtual prototyping, through static and formal verification, to simulation, emulation and FPGA-based prototyping. The verification problem space is simply too big, in size certainly but also in dynamic range, to be effectively addressed… Read More

35 Semiconductor IP Companies Hold 2nd Annual Conference

Our smart phone driven semiconductor economy consumes a lot of IP blocks to enable quick product development cycles, often annually updating with new models to choose from. So where do you find all of the best semiconductor IP, verification IP and embedded software? Well, one place is at the 2nd annual REUSE conference, scheduled… Read More

What are you ready to mobilize for FPGA debug?

There are 3 common misconceptions about debugging FPGA with the real hardware:

[LIST=1]

RISC-V Business

I was at the 7[SUP]th[/SUP] RISC-V Workshop for two days this week. It was hosted by Western Digital at their headquarters in Milpitas. If you have not been following RISC-V, it is an open source Instruction Set Architecture (ISA) for processor design. The initiative started at Berkeley, and has been catching on like wildfire. … Read More

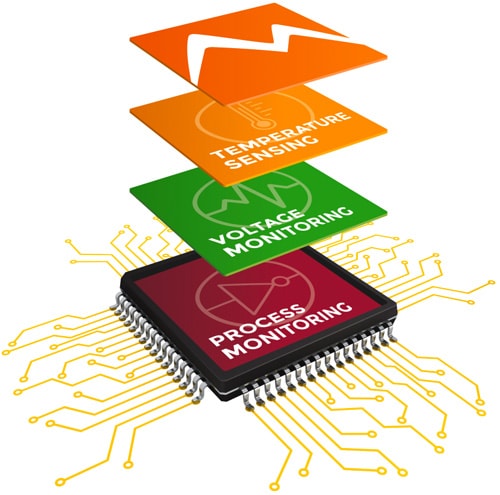

Making Your Next Chip Self-Aware

One holy grail of AI software developers is to create a system that is self-aware, or sentient. A less lofty goal than sentient AI is for chip designers to know how each specific chip responds to Process variations, Voltage levels and Temperature changes. If a design engineer knew exactly which process corner that each chip was fabricated… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center