The year is 2005 and PMC Sierra decided that it is time to expand by adding a new site in Bangalore, India. We started with digital verification first but by 2006 we were ready to engage with Mixed Signal Design and Layout. I went to Bangalore in June 2006 for the first time and with the help of our local manager, Vikram Labhe, had a few layout… Read More

Electronic Design Automation

Mentor Siemens Update 2018

As you know I am a big fan of disruption and the Siemens acquisition of Mentor is turning out to be one of my favorite EDA disruptions. At first it was a little bit perplexing but after one short year it makes complete sense.

Siemens is acquiring Mentor as part of its Vision 2020 concept to be the Benchmark for the New Industrial Age. It’s… Read More

CEO Interview: Jason Oberg of Tortuga Logic

I first met Jason Oberg, CEO and one of the co-founders of Tortuga Logic, several years ago when I was still at Atrenta. At that time Jason and Jonny Valamehr (also a co-founder and the COO) were looking for partners. The timing wasn’t right, but we’ve stayed in touch, for my part because their area of focus (security) is hot and likely… Read More

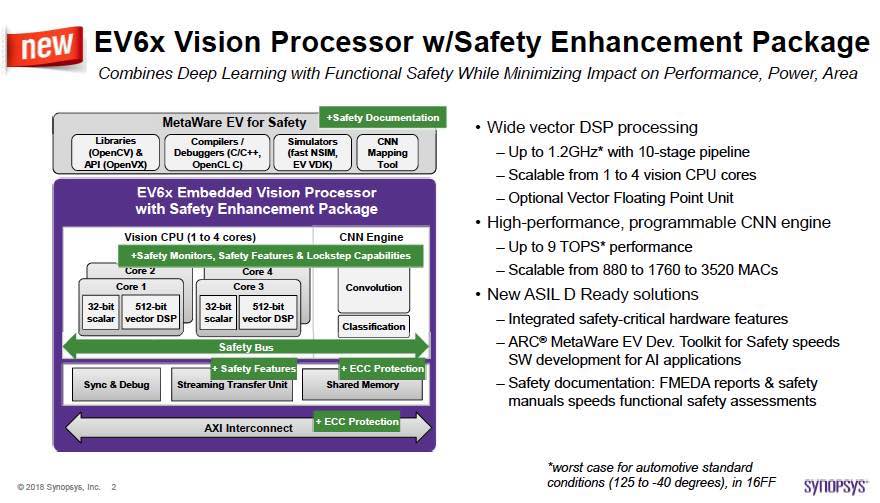

ISO 26262 First – ASIL-D Ready Vision Processor IP Available

Synopsys made a pretty major announcement regarding their new ASIL-B,C and D ready embedded vision processor IP. This matters because you cannot bolt on the design elements and features needed to achieve these ASIL levels later, and this IP is absolutely necessary for ADAS systems and other critical safety systems in automobiles.… Read More

Innovation in a Commodity Market

Logic simulation is a victim of its own success. It has been around for at least 40 years, has evolved through multiple language standards and has seen significant advances in performance and major innovations in testbench standards. All that standardization and performance improvement has been great for customers but can present… Read More

Should EDA Follow a Foundry Model?

There is an interesting discussion in the SemiWiki forum about EDA and the foundry business model which got me to thinking about the next disruptive move for the semiconductor industry. First let’s look at some of the other disruptive EDA events that I experienced firsthand throughout my 30+ year career.

When I started in 1984 EDA… Read More

Webinar: IP Quality is a VERY Serious Problem

We just completed a run through of the upcoming IP & Library QA webinar that I am moderating with Fractal and let me tell you it is a must see for management level Semiconductor Design and Semiconductor IP companies as well as the Foundries. Seriously, if you are an IP company you had better be up on the latest QA checks if you want … Read More

Welcome DDR5 and Thanks to Cadence IP and Test Chip

Will we see DDR5 memory (device) and memory controller (IP) in the near future? According with Cadence who has released the first test chip in the industry integrating DDR5 memory controller IP, fabricated in TSMC’s 7nm process and achieving a 4400 megatransfers per second (MT/sec) data rate, the answer is clearly YES !

Let’s come… Read More

Managing Your Ballooning Network Storage

As companies scale by adding more engineers, there is a tendency to spread across multiple design sites as they strive to hire the best available talent. Multi-site development also impacts startups as they try to minimize their burn rate by having an offsite design center such as India, China or Vietnam.

Both the IoT and automotive… Read More

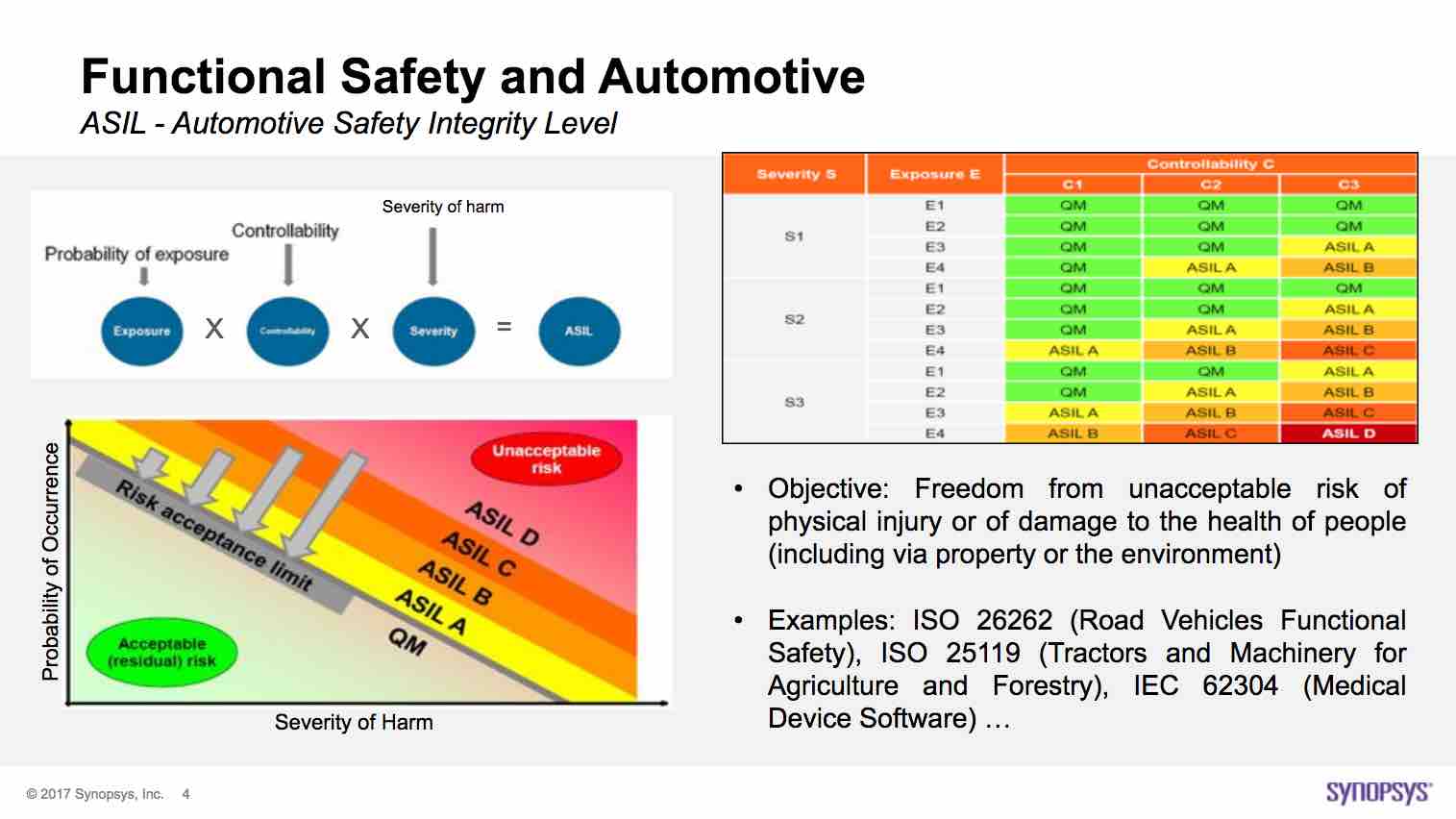

Functional Safety is a Driving Topic for ISO 26262

When I was young, functional safety for automobiles consisted of checking tread depth and replacing belts and hoses before long trips. I’ll confess that this was a long time ago. Though even not that long ago, the only way you found out about failing systems was going to the mechanic and having them hook up a reader to the OBD port. Or,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center