This article will describe the motivations for pursuing a new flow in the SoC design methodology. This flow involves the extraction, evaluation, and analysis of a full electromagnetic coupling model for a complex SoC and its package environment. The results of this analysis highlight the impact of electromagnetic coupling… Read More

Electronic Design Automation

It’s The Small Stuff That Gets You …

The last session I attended at DesignCon 2020 wasn’t a session at all. Rather it was an interactive discussion with Todd Westerhoff, product manager for electronic board systems at Mentor Graphics. Todd made some observations about the way high-performance PCBs are designed today and perhaps the way they should be designed. … Read More

AI Interposer Power Modeling and HBM Power Noise Prediction Studies

I attended a session on 2.5D silicon interposer analysis at DesignCon 2020. Like many presentations at this show, ecosystem collaboration was a focus. In this session, Jinsong Hu (principal application engineer at Cadence) and Yongsong He (senior staff engineer at Enflame Tech) presented approaches for interposer power modeling… Read More

Executive Interview: Howie Bernstein of HCL

Howie began his career at Digital Equipment Corporation working on real-time device drivers, but within a few years started working at the other end of the stack with one of the pioneering electronic mail systems. Since then, Howie has worked on developing systems involving electronic mail, workflow processing, configuration… Read More

Verification, RISC-V and Extensibility

RISC-V is obviously making progress. Independent of licensee signups and new technical offerings, the simple fact that Arm is responding – in fundamental changes to their licensing model and in allowing custom user extensions to the instruction set – is proof enough that they see a real competitive threat from RISC-V.

Which all… Read More

Signal Channel Design and Simulation for Silicon Interposer Packaging on High-Speed SerDes

This year is the 25th anniversary for DesignCon. The show has changed a lot over the years. Today, it’s a vibrant showcase of all aspects of advanced product design – from ICs to boards to systems. The show floor reflects the diverse ecosystem. If you missed it this year, definitely plan to go next year.

The DesignCon technical program… Read More

Bringing Hierarchy to DFT

Hierarchy is nearly universally used in the SoC design process to help manage complexity. Dealing with flat logical or physical designs proved unworkable decades ago. However, there were a few places in the flow where flat tools continued to be used. Mentor lead the pack in the years around 1999 in helping the industry move from … Read More

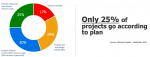

How Good is Your Testbench?

I’ve always been intrigued by Synopsys’ Certitude technology. It’s a novel approach to the eternal problem of how to get better coverage in verification. For a design of any reasonable complexity, the state-space you would have to cover to exhaustively consider all possible behaviors is vastly larger than you could ever possibly… Read More

Formal and High-Level Synthesis

Formal verification has made significant inroads in RTL and gate-level verification because it provides complementary strengths to conventional dynamic verification methods; using both provides higher levels of coverage and confidence in the correctness of an implementation. I haven’t heard as much about formal use in … Read More

Innovation in Verification – January 2020

I’m kicking off a blog series which should appeal to many of us in functional verification. Paul Cunningham (GM of the Verification Group at Cadence), Jim Hogan (angel investor and board member extraordinaire) and I (sometime blogger) like to noodle from time to time on papers and other verification articles which inspire us.… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era