Many years ago, digital and analog design flows diverged, with digital design benefiting from increasing levels of automation and more importantly separation between the front-end design process and the back-end design process. While digital design still requires linkages between the front and back end, they are well defined… Read More

Electronic Design Automation

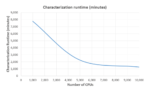

Library Characterization: A Siemens Cloud Solution using AWS

Pressing demands on compute speeds, storage capacity and rapid access to data are not new to the semiconductor industry. A desire for access to on-demand computing resources have always been there. During pre-cloud-computing era, companies provisioned on-demand compute capacity by procuring high performance computing … Read More

Why Would Anyone Perform Non-Standard Language Checks?

The other day, I was having one of my regular chats with Cristian Amitroaie, CEO and co-founder of AMIQ EDA. One of our subjects was a topic that we discussed last year, the wide range of languages and formats that chip design and verification engineers use these days. AMIQ EDA has put a lot of effort into adding support for many of these… Read More

Podcast EP13: The Three Pillars of Verification with Adnan Hamid

Dan goes on a scenic tour of verification with Adnan Hamid, founder and CEO of Breker Verification Systems. We discuss the rather unusual way Adnan got into semiconductors and SoC verification. Adnan then breaks down the verification task into its fundamental parts to reveal what the three pillars of verification are and why … Read More

Reducing Compile Time in Emulation. Innovation in Verification

Is there a way to reduce cycle time in mapping large SoCs to an FPGA-based emulator? Paul Cunningham (GM, Verification at Cadence), Jim Hogan (RIP) and I continue our series on research ideas. As always, feedback welcome.

The Innovation

This month’s pick is Improving FPGA-Based Logic Emulation Systems through Machine Learning… Read More

Smarter Product Lifecycle Management for Semiconductors

Product Lifecycle Management (PLM) for electronic systems has moved from a passive ‘fire and forget’ approach to one that is intimately involved not only during design, but also throughout the entire life of every unit delivered to the field. Siemens EDA has a white paper titled “Tessent Silicon Lifecycle Solutions” that talks… Read More

SoC Integration – Predictable, Repeatable, Scalable

On its face System-on-chip (SoC) integration doesn’t seem so hard. You gather and configure all the intellectual properties (IPs) you’re going to need, then stitch them together. Something you could delegate to new college hires, maybe? But it isn’t that simple. What makes SoC integration challenging is that there are so many… Read More

Observation Scan Solves ISO 26262 In-System Test Issues

Automotive electronic content has been growing at an accelerating pace, along with a shift from infotainment toward mission critical functions such as traction control, safety systems, engine control, autonomous driving, etc. The ISO 26262 automotive electronics safety standard evolved to help ensure that these systems… Read More

The Electromagnetic Solution Buyer’s Guide

So you’ve decided to buy a new car? First you need to research, compare, and test drive before you finally get to drive that shiny new car home. Engineering teams choosing their preferred electromagnetic analysis tool face similar challenges. Historically, electromagnetic problems and analysis tools were relegated to a few … Read More

Siemens EDA Wants to Help you Engineer a Smarter Future Faster

In case you missed it earlier this year, Mentor Graphics the oldest EDA brand officially changed its name to Siemens EDA and launched a new website under its parent Siemens Digital Industries Software.

Under Siemens Digital Industries Software, Siemens EDA adds IC, advanced IC packaging and PCB systems design, verification/validation… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era