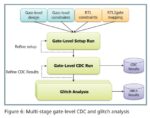

Glitches on clock domain crossing signals have always been a concern for chip designers. Now with increased requirements for reliability, renewed scrutiny is being given to find ways to identify these problems and fix them. In particular applications such as automotive electronics have given this added effort an impetus. Siemens… Read More

Electronic Design Automation

Keynote from Air Force Research Laboratory at CadenceLIVE Americas 2021

Cadence hosted its annual CadenceLIVE Americas conference June 8th-June 9th. Four keynotes and eighty-three different talks on various topics were presented. The talks were delivered by Cadence, its customers and partners.

The C-suite keynotes were delivered by Lip-Bu Tan (CEO) and Dr. Anirudh Devgan (President). The talks… Read More

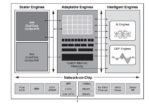

Circuit Simulation Challenges to Design the Xilinx Versal ACAP

One of the most unique acronyms that I learned about this past year is ACAP from Xilinx, which stands for Adaptive Compute Acceleration Platform. At the recent Cadence LIVE event, I had the pleasure of watching Pei Yao, a Xilinx senior staff CAD engineer, as she talked about the challenges of getting all the analog and mixed-signals… Read More

Cadence Keynotes at CadenceLIVE Americas 2021

Last week, Cadence hosted its annual CadenceLIVE Americas conference. Four keynotes and eighty-three different talks on various topics were presented. The talks were delivered by Cadence, its customers and partners.

This blog is about the two keynotes delivered by CEO Lip-Bu Tan and President Dr. Anirudh Devgan. The guest … Read More

Life in a Formal Verification Lane

This summer, I got the opportunity to work as a Formal Verification Intern with Axiomise for six weeks. I’m a keen designer and love working in design and architecture. Although, I’ve not started my professional career yet, I have done most of my projects as a designer in my undergraduate and postgraduate studies.

Having said that,… Read More

EDA Design and Amazon Web Services (AWS)

I first remember blogging about EDA in the cloud starting back in 2011, so what’s changed in the last 10 years you may ask? In 2011, it was basically a handful of EDA point tools running batch mode in the cloud, and you were on your own to integrate those into a coherent flow, so expect help from the CAD and IT departments for sure.… Read More

Die-to-Die Connections Crucial for SOCs built with Chiplets

If you ascribe to the notion that things move in circles, or concentrically, the move to die-to-die connectivity makes complete sense. Just as multi-chip modules (MCM) were the right technology decades ago to improve power, areas, performance and cost, the use of chiplets with die-to-die connections provides many advantages… Read More

There’s No Such Thing as Ground (But Perhaps There’s a Bob) Minimze Your Ports

I would contend there is no job quite like working as a support engineer for a simulation tool like Ansys HFSS. Such a role forces an engineer to understand technology in breadth and depth like no other because HFSS is applied to such a broad range of applications and products throughout the world. My own introduction to HFSS began … Read More

Connecting System Design to the Enterprise

While systems design underpins the explosion in “smart everything”, it remains somewhat isolated from another explosion—the proliferation of tools for application lifecycle management (ALM). ALM tools are prevalent on the web, in the cloud and on our phones, to streamline product design and build, to track correspondence… Read More

Keynote from Google at CadenceLIVE Americas 2021

Last week, Cadence hosted its annual CadenceLIVE Americas 2021 conference. Four keynotes and eighty-three different talks on various topics were presented. The talks were delivered by Cadence, its customers and partners.

One of the keynotes was from Partha Ranganathan, VP and Engineering Fellow from Google. His talk was titled,… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era