Lauro Rizzatti recently interviewed Jean-Marie Brunet, vice president of product management and product engineering in the Scalable Verification Solution division at Siemens EDA, about why hardware-assisted verification is a must have for today’s semiconductor designs. A condensed version of their discussion is below.… Read More

Electronic Design Automation

DAC 2021 – What’s Up with Agnisys and Spec-driven IC Development

Walking the exhibit floors at DAC in December I spotted the familiar face of Anupam Bakshi, Founder and CEO of Agnisys, so I stopped by the booth to get an update on his EDA company. My first question for him was about the origin of the company name, Agnisys, and I found at that Agni means Fire in Sanskrit, one of the five elements.

The … Read More

Can you Simulate me now? Ansys and Keysight Prototype in 5G

Ansys and Keysight wanted to see if they could answer the question, If we put virtual cellphones in different locations in a city, can we predict what kind of 5G signal we’re going to get in those locations? To find out, they created and tested a detailed virtual model of a city, including a variety of 5G antennae, receivers, and transmitters… Read More

Identity and Data Encryption for PCIe and CXL Security

Privacy and security have always been a concern when it comes to computing. In prior decades for most people this meant protecting passwords and locking your computer. However, today more and more users are storing sensitive data in the cloud, where it needs to be protected at rest and while in motion. In a Synopsys webinar Dana Neustadter,… Read More

Cliosoft and Microsoft to Collaborate on the RAMP Program

We have all heard of many advanced technological inventions and products from the defense sector that subsequently got commercialized. While most of the Defense Advanced Research Projects Agency (DARPA) projects are classified secrets, many military innovations have had great influence in the commercial sector in the fields… Read More

Webinar: AMS, RF and Digital Full Custom IC Designs need Circuit Sizing

My career started out by designing DRAM circuits at Intel, and we manually sized every transistor in the entire design to get the optimum performance, power and area. Yes, it was time consuming, required lots of SPICE iterations and was a bit error prone. Thank goodness times have changed, and circuit designers can work smarter … Read More

White Paper: A Closer Look at Aging on Clock Networks

We all know that designers work hard to reach design closure on SOC designs. However, what gets less attention from consumers is the effort that goes into ensuring that these chips will be fully operational and meeting timing specs over their projected lifetime. Of course, this is less important for chips used in devices with projected… Read More

DAC 2021 – Cliosoft Overview

It’s been awhile since I really looked at what Cliosoft has to offer in the EDA tool space, so at the 58th DAC I stopped by their exhibit booth on Tuesday to visit with Karim Khalfan, VP of Application Engineering, and Simon Rance, VP of Marketing. Their booth had all of the hot market segments listed: Automotive, 5G, IoT, AI, … Read More

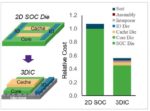

Heterogeneous Integration – A Cost Analysis

Heterogeneous integration (HI) is a general term used to represent the diverse possibilities for die technology incorporated into advanced 2.5D/3D packaging. At the recent International Electron Devices Meeting (IEDM) in San Francisco, a team from Synopsys and IC Knowledge presented data from analyses of future potential… Read More

Methodology for Aging-Aware Static Timing Analysis

At the recent Design Automation Conference, Cadence presented their methodology for incorporating performance degradation measures due to device aging into a static timing analysis flow. [1] (The work was a collaborative project with Samsung Electronics.) This article reviews the highlights of their presentation.

Background… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era