Author: Niranjan Sitapure, AI Product Manager, Siemens EDA

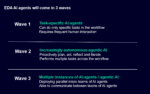

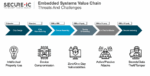

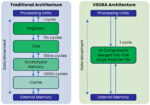

We are at a pivotal point in Electronic Design Automation (EDA), as the semiconductors and PCB systems that underpin critical technologies, such as AI, 5G, autonomous systems, and edge computing, grow increasingly complex. The traditional EDA workflow, which includes… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior