In the semiconductor design industry, most of the designs are created and optimized at the RTL level, mainly through home grown scripts or manual methods. As there can be several iterations in optimizing the hierarchy for physical implementation, it’s too late to do the hierarchical optimizations after reaching the floor plan… Read More

Author: Pawan Fangaria

Crossfire – Your partner for IP development, what’s new?

As the SoCs and IPs grow in sizes and complexities, the number of formats, databases, libraries of standard cells and IOs also increase. It becomes a clumsy task to check every cell in a library, its consistency among various format with respect to functionality, timing, naming, labels and so on, and its complex physical properties… Read More

Vlang – Opportunities Galore for Productivity & Performance

Yes, verification technologies are open to innovation for improved productivity and performance in the face of ever growing SoC/IP design sizes and complexities. There is not much scope left in processor speed to improve, other than multi-core processors in servers which again need software properly architected to be thread-able… Read More

How to Reduce Maximum Power at RTL Stage?

Of course that reduction has to stay throughout the design cycle up to layout implementation and fabrication. Since the advent of high density, mega functionality SoC designs at advanced nodes and battery life critical devices played by our fingertips, the gap between SoC power requirement and actual SoC power has only increased.… Read More

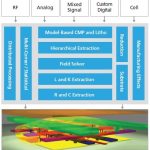

A Deeper Insight into Quantus QRC Extraction Solution

Last month Cadenceannounced its fastest parasitic extraction tool (minimum 5 times better performance compared to other available tools) which can handle growing design sizes with interconnect explosion, number of parasitics and complexities at advanced process nodes including FinFETs, without impacting accuracy of … Read More

Wanna start something new? Try this…

Often I have been asked by students, researchers and buddying young entrepreneurs about sources of funds for new technology development and innovation. When I came across this wonderful opportunity which has a global appeal, I couldn’t resist myself bringing it to the notice of a wider audience. I admire nVIDIA supporting research… Read More

Analog Model Equivalence Checking Accelerates SoC Verification

In the race to reduce verification time for ever growing sizes of SoCs, various techniques are being adopted at different levels in the design chain, functional verification being of utmost priority. In an analog-digital mixed design, which is the case with most of the SoCs, the Spice simulation of analog components is the limiting… Read More

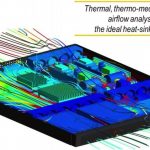

Electronic Thermal Management through Icepak

Last week my daughter was playing some games on my Google Nexus smartphone for a while when one of my friends called. When I picked up the phone, I couldn’t imagine it was so hot. There is no doubt; every electronic device today emits an order of magnitude higher heat than what it used to at most a decade ago. There is so much emphasis on … Read More

Enabling Higher Level Design Automation with Smart Tools

Although design houses have always strived for optimizing best design flows according to their design needs by customizing the flows using effective and efficient internal as well as external tools, this need has further grown in the context of design scenarios getting wider and wider from transistor, gate and RTL to system level.… Read More

It’s not a fiction, it’s about to turn into reality

Often I used to wonder why a search engine company would invest so heavily and indulge into stuff like smartphones, home automation devices, servers and many other exotic, innovative things they are doing internally and externally. But when I connect the dots, I find that this company in on certain massive missions which, if accomplished… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center