An informal survey of RTDA customers reveals that larger companies tend to buy licenses based on peak usage while smaller companies do not have that luxury and have to settle for fewer licenses than they would ideally have and optimize the mix of licenses that they can afford given their budget. Larger companies get better prices… Read More

Author: Paul McLellan

EUV: No Pellicle

There’s a dirty secret problem about EUV that people don’t seem to to be talking about. There’s no pellicle on a EUV mask. OK, probably you have no idea what that means, a lot of jargon words, nor why it would be important, but it seems to me it could be the killer problem for EUV.

In refractive masks, you print a pattern… Read More

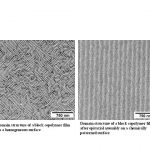

Directed Self Assembly

At Semicon, Ben Rathsack of Tokyo Electron America talked about directed self assembly (DSA) at the standing-room only lithography morning. So what is it? Self assembly involves taking two monomers that don’t mix and letting them polymerise (so like styrene forming polystyrene). Since they won’t mix they will … Read More

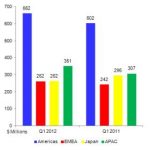

EDAC Announces EDA up 6.3% in Q1 versus 2011

EDAC announced that EDA industry revenue increased 6.3% for Q1 2012 to $1536.9M compared to a year ago. Sequentially it declined, as it normally does from Q4 to Q1, by 9.6%. Every category except services increased revenue and every region increased revenue except for Japan. The full report is available by subscription, of course.… Read More

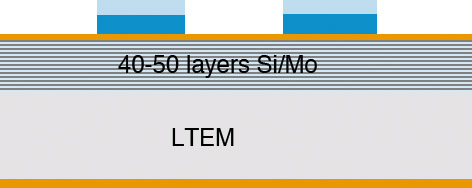

EUV Masks

This is really the second part to this blog about the challenges of EUV lithography. The next speaker was Franklin Kalk who is CTO of Toppan Photomasks. He too emphasized that we can make almost arbitrarily small features but more and more masks are required (not, that I suspect, he would complain being in the mask business). For EUV… Read More

3D Thermal Analysis

Matt Elmore of ANSYS/Apache has an interesting blog posting about thermal analysis in 3D integrated circuits. With both technical and economic challenges at process nodes as we push below 28nm, increasingly product groups are looking towards through-silicon-via (TSV) based approaches as a way of keeping Moore’s law… Read More

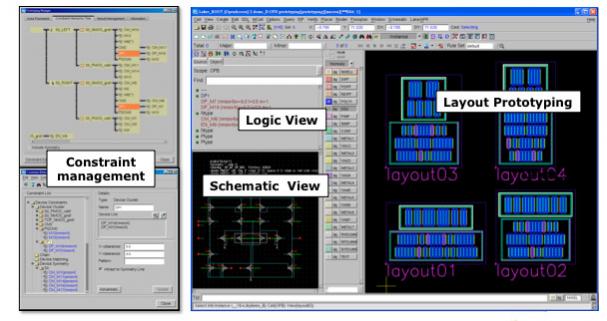

Laker Analog Prototyping

Over the years many attempts have been made to increase the level of automation in analog design. Most of these have not been especially successful. Probably part of the reason was inadequate technology but also there is an attitude that “real” analog designers design polygons on the bare silicon. I think two things… Read More

Extreme Ultra Violet (EUV)

EUV is the great hope for avoiding having to go to triple (and more) patterning if we have to stick with 193nm light. There were several presentations at Semicon about the status of EUV. Here I’ll discuss the issues with EUV lithography and in a separate post discuss the issues about making masks for EUV.

It is probably worth … Read More

Silicon on Insulator (SOI)

I attended a panel session followed by a party during Semicon to celebrate Soitec’s 20th birthday. Officially it was titled An Insider’s Look at the Future of Mobile Technologies. But in reality it was a look at the future possibilities for SOI.

Silicon on Insulator (SOI) has been a sort of bastard child of semiconductor.… Read More

Direct Write E-beam

One of the presenters at the standing-room only litho session at Semicon this week was Serge Tedesco, the litho program manager at CEA-Leti in Grenoble France. He is running a program called IMAGINE for maskless lithography. Chips today are built using a reticle (containing the pattern for that layer of the chip) which is exposed… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era